エリアアレイ表面実装パッケージ(BGA)のロードマップ:福田昭のデバイス通信(441) 2022年度版実装技術ロードマップ(65)

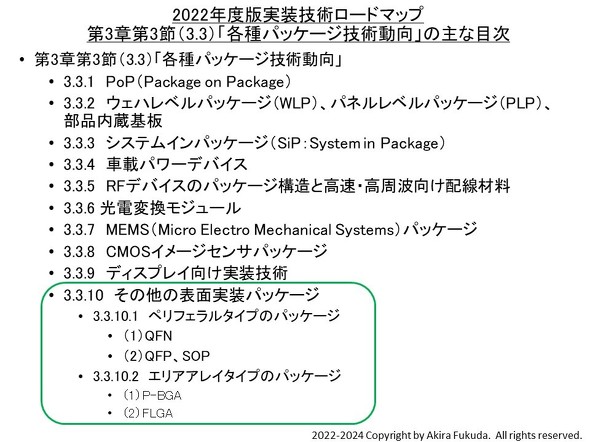

今回は、第3章第3節第10項(3.3.10)「その他の表面実装パッケージ」の概要を説明する。

ペリフェラルタイプとエリアアレイタイプの表面実装パッケージ

電子情報技術産業協会(JEITA)が3年ぶりに実装技術ロードマップを更新し、「2022年度版 実装技術ロードマップ」(書籍)を2022年7月に発行した。本コラムではロードマップの策定を担当したJEITA Jisso技術ロードマップ専門委員会の協力を得て、ロードマップの概要を本コラムの第377回からシリーズで紹介している。

前々回と前回は、第3章第3節第5項(3.3.5)「RFデバイスのパッケージ構造と高速・高周波向け配線材料」の概要を前後編で報告した。今回は、第3章第3節第10項(3.3.10)「その他の表面実装パッケージ」の概要をご説明する。

「3.3.10 その他の表面実装パッケージ」は、「3.3.10.1 ペリフェラルタイプのパッケージ」と「3.3.10.2 エリアアレイタイプのパッケージ」で構成される。ペリフェラルタイプとは、パッケージ本体の周辺に端子を配列したタイプのパッケージを指す。代表的なペリフェラルタイプのパッケージにはQFN(Quad Flat Non-leaded package)、QFP(Quad Flat Package)、SOP(Small Outline Package)などがある。

QFNはパッケージの四辺に端子電極を配置したパッケージで、外部リード端子を持たないのでQFPやSOPなどに比べて実装面積が小さくて済む。また実装高さは最小で0.35mmと低く、低背化が図れる。現在は50ピン以下の少ピン品が多く使われている。この傾向は今後も変わらないとみられる。

QFPとSOPは高さが最小0.8mm、端子ピッチが最小0.4mm、最大端子数は256ピン(QFP)と64ピン(SOP)となっている。この仕様は2031年になっても変わらない。QFPの256ピンよりも多いピン数は、エリアアレイタイプのパッケージがカバーしている。

エリアアレイタイプとは、パッケージ本体の底面に端子を2次元マトリクス状に配置したタイプのパッケージを指す。代表的なエリアアレイタイプのパッケージにはBGA(Ball Grid Array)やLGA(Land Grid Array)などがある。

プラスチックBGAの多ピン化が進み、2031年には7200ピンへ

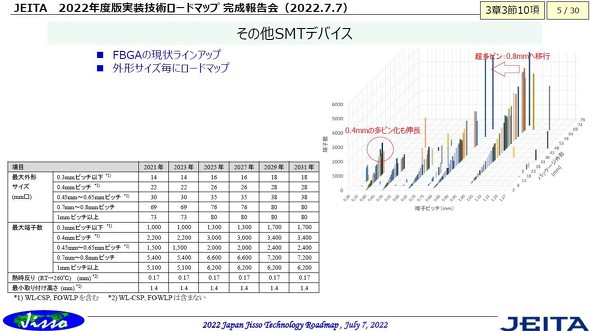

BGAには樹脂基板のプラスチックBGAとセラミック基板のセラミックBGAがある。主流はプラスチックBGAであり、従来型の表面実装パッケージを代表する存在となっている。端子ピッチは0.3mm以下から1mm以上まで幅広い。外形寸法は14mm角〜73mm角とこれも幅広く存在する。

プラスチックBGAのロードマップ。右上は現在(2021年)の端子ピッチと外形寸法、最大端子数の関係を棒グラフで表現したもの。左下は最大外形寸法と最大端子数のロードマップ(2021年〜2031年)。端子ピッチ別に記述してある。出所:JEITA Jisso技術ロードマップ専門委員会(2022年7月7日に開催された完成報告会のスライド)[クリックで拡大]

端子数で5000ピンを超えるような超多ピン領域は、はんだ付けの難易度から端子ピッチ0.8mmあるいは1.0mmクラスのプラスチックBGAが使われる。端子ピッチが0.3mm以下のBGAははんだ付けが難しくなることから、ピン数は1000ピン以下にとどまっている。

端子ピッチ別に最大端子数の将来を予測していくと、2031年に0.3mm以下は1700ピン(2021年は1000ピン)、0.4mmは3400ピン(2021年は2200ピン)、0.45〜0.65mmは2400ピン(2021年は1500ピン)、0.7〜0.8mmは7200ピン(2021年は5400ピン)、1.0mm以上は6200ピン(2021年は5100ピン)となる見込みである。多ピン化が今後もかなり進行することが分かる。

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

4Gから5Gミリ波の移動体通信向けフロントエンドパッケージ(後編)

4Gから5Gミリ波の移動体通信向けフロントエンドパッケージ(後編)

後編となる今回は、誘電体材料パターニング方法とAiP(Antenna in Package)の概要を紹介する。 車載パワーデバイスの出力密度向上手法

車載パワーデバイスの出力密度向上手法

今回は、第3章第3節第4項「車載パワーデバイス」から、「パワーデバイスの発展」を解説する。 プリント基板に半導体チップを埋め込む部品内蔵基板

プリント基板に半導体チップを埋め込む部品内蔵基板

今回は、FO-WLP(Fan Out-Wafer Level Package)のロードマップと、FO-PLP(Fan Out-Panel Level Package)の一種ともみなせる部品内蔵基板について解説する。 多ピン小型パッケージ「FO-WLP」の信頼性問題とその対策

多ピン小型パッケージ「FO-WLP」の信頼性問題とその対策

今回は初期の「FO-WLP」で生じた信頼性の問題と、問題を解決した組み立てプロセス、再配線層(RDL)を微細化したプロセスを解説する。 超多ピンと複数ダイ搭載を両立させた小型パッケージFO-WLP

超多ピンと複数ダイ搭載を両立させた小型パッケージFO-WLP

引き続き、各種パッケージ技術の動向を紹介する第3章第3節を取り上げる。今回から「3.3.2.2 FO-WLP、FO-PLP、部品内蔵基板」の概要を紹介する。 表面実装工程の省エネに寄与する低融点の鉛フリーはんだ

表面実装工程の省エネに寄与する低融点の鉛フリーはんだ

今回は、第2章第6節第6項「2.6.6 接合材料」から、「SMT(Surface Mount Technology)における接合材料の現状と課題」の概要を紹介する。