拡張可能な全結合型イジングプロセッサを開発:複数の22nm CMOSチップで構成

東京理科大学は、複数の22nm CMOSチップを用いて、拡張可能な「全結合半導体イジングプロセッシングシステム」を開発した。2030年までには200万スピンという大規模化を目指す。

2030年までには200万スピンの実現目指す

東京理科大学工学部電気工学科の河原尊之教授の研究グループは2024年3月、複数の22nm CMOSチップを用いて、拡張可能な「全結合半導体イジングプロセッシングシステム」を開発したと発表した。2030年までには200万スピンという大規模化を目指す。

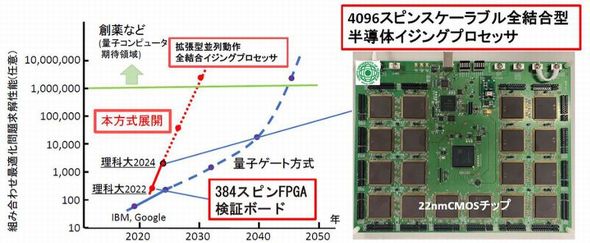

集積回路で実現するイジングマシンは、「組み合わせ最適化問題」を従来のコンピュータに比べ高速に解くことができる。河原教授らは2020年に、28nm CMOS技術を用い独自アーキテクチャの全結合型LSIを1チップで実現した。2022年には、並列動作させた複数チップを用いて、拡張可能な全結合型方式を考案。FPGAを活用して384スピンの全結合アニーリング処理イジングシステムボードを作成した。

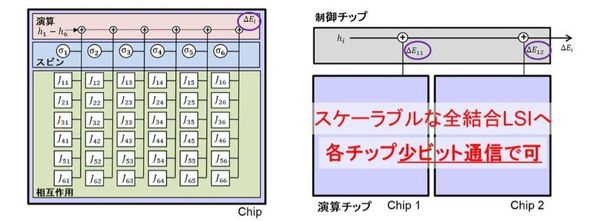

そして今回、22nm CMOS技術を用いて製造した演算用のLSIチップ36個と、制御用のFPGA1個を組み合わせ、4096スピンを持つスケーラブル全結合型イジングプロセッサシステムを開発した。このシステムでは独自開発の「相互作用半減実装方式」と「スピンスレッド」を採用している。相互作用半減実装方式により、必要なチップ数を従来に比べほぼ半分に減らした。また、スピンスレッドを8個搭載しており、1回のデータ出し入れで8回分の計算を1度に行えるという。

開発したシステムは10MHzで動作する。ボード全体の消費電力は2.9Wで、このうち演算LSIチップ36個分が消費する電力は1.3Wである。研究グループは開発したステムを用い、「4096頂点の頂点被覆問題」を解いた。この結果、全結合イジングシステムを模したアニーリングエミュレーションを、動作周波数3.6GHzのCPUを搭載したPCで実行した場合に比べ、2306倍という高いエネルギー効率が得られた。コア部同士(CPUと演算チップ)の比較でも、2186倍の電力性能比となった。しかも、スピンスレッドを用いた8並列のため、精度の高い探索が可能である。

研究グループは、2030年までに200万スピンを実現していく予定。これによって、量子コンピュータが2050年ごろに到達するといわれている性能と同等性能を、2030年には達成できる可能性があるという。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

顔の映像から心拍数を高精度に推定する手法を開発

顔の映像から心拍数を高精度に推定する手法を開発

東京理科大学、津田塾大学らの研究グループは2023年8月7日、顔の映像から非接触/高精度で心拍数を推定する新手法を開発したと発表した。従来法よりも推定精度が36.5%向上したという。 神経系の動作をマネ、高速動作の電気二重層トランジスタ

神経系の動作をマネ、高速動作の電気二重層トランジスタ

物質・材料研究機構 (NIMS)と東京理科大学の研究チームは、セラミックス薄膜とダイヤモンドを用い、従来に比べ8.5倍も高速動作する電気二重層トランジスタを開発した。このトランジスタはニューロモルフィック動作を高速かつ高い精度で行えるという。 東京理科大、全固体酸化還元型トランジスタを開発

東京理科大、全固体酸化還元型トランジスタを開発

東京理科大学らの研究グループは、リチウムイオン伝導性ガラスセラミック基板上にタングステン酸リチウム薄膜を積層した「全固体酸化還元型トランジスタ」を開発した。この素子を物理リザバーに用いれば、機械学習を高速かつ低消費電力で実行できる「ニューロモルフィックコンピューティング」技術を実現できるという。 偏光空間構造を用い、スピンの空間構造を直接生成

偏光空間構造を用い、スピンの空間構造を直接生成

東京理科大学と千葉大学、東北大学、筑波大学の研究グループは、ラゲールガウシアンビームの一種である「ベクトル光渦」と呼ばれる偏光の空間周期構造を、スピンの空間周期構造として半導体量子井戸中へ直接生成することに成功した。 高伝導率の配線をPP基板上に直接作製する技術を開発

高伝導率の配線をPP基板上に直接作製する技術を開発

東京理科大学は、大気圧下の室温で直接プラスチックフィルム上に多層カーボンナノチューブ(MWNT)配線を行うことができる新たな方法を開発した。レーザーを照射する条件によって、MWNT配線の抵抗値や線幅を変えることもできるという。 全固体リチウム電池、中間層挿入で応答速度を改善

全固体リチウム電池、中間層挿入で応答速度を改善

東京理科大学と物質・材料研究機構(NIMS)の研究チームは、全固体リチウム電池の電気二重層容量を制御することで、充電時のスイッチング応答速度を大幅に改善させることに成功した。