アナログICを薄膜化して3次元積層、レガシープロセスで:日清紡マイクロデバイスとOKIが共同開発(3/3 ページ)

日清紡マイクロデバイスと沖電気工業(OKI)が、アナログICをわずか数ミクロンに薄膜化し、それを3次元積層することに成功した。2026年の量産化を目指す。

ライセンス提供などのビジネスモデルも検討

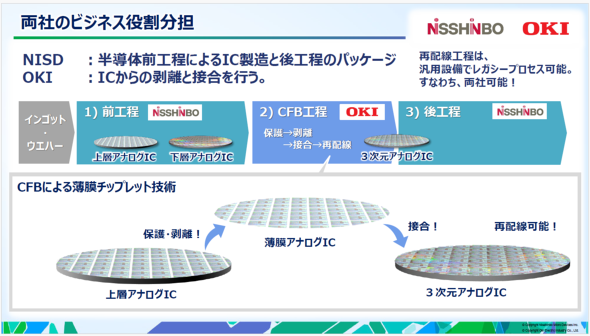

ビジネスモデルとしては、前工程を日清紡マイクロデバイスが担当する。このとき、機能層に形成したアナログICをCFB技術で剥離できるような成膜プロセスを行う必要がある。OKIは、上層アナログICと下層アナログICのウエハーを受け取り、CFB技術で剥離、接合(積層)する。その後、日清紡マイクロデバイスが後工程を行う。

ただし両社は今後、同技術をライセンスとして提供したり、日清紡マイクロデバイスとOKIにもう1社を加えた3者連携や、パートナーシップ締結による製造など、あらゆる形態を探っていくという。

まずは、日清紡マイクロデバイスが保有する既存プロセスで、2026年内の量産化を目指す。現時点では具体的な製品などは決まっていないが、あらゆるアナログICを組み合わせることが可能だという。「さまざまなローエンドアナログICを集積化して試してみたい」(日清紡マイクロデバイス)

自動運転やADAS(先進支援運転システム)などでセンサーの数が増加する中、センサーからの信号処理を担うアナログICのニーズも増している。アナログICの世界市場は、2023年の12兆円から、CAGR7.3%で成長し、2028年には17兆円に達する見込みだという。同時に、アナログICのさらなる小型化と高性能化を実現するために、集積度を上げるニーズも高まっているのが現状だ。

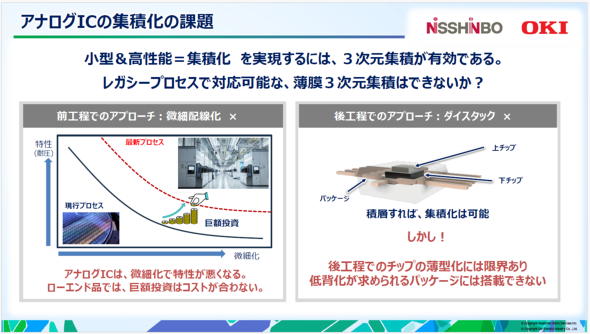

ただし、アナログICの集積化には多くの課題がある。アナログICは扱う電圧が20Vや30Vなどと高いので、基本的に耐圧が低くなる微細化では特性が悪くなってしまう(高い電圧が扱えなくなる)。さらに、アナログICはローエンド品も多く、巨額の設備投資を行って最先端の製造装置を導入するのはコストが見合わない。ロジック半導体のように積層するにも、アナログICの薄型化には限界があり、低背化が求められるパッケージには搭載が難しい。このように、前工程、後工程、どちらのアプローチでもアナログICの集積は難しかった。これに対して、レガシープロセスでも集積できるようにしたのが、今回の両社の取り組みだ。

緒方氏は、「積層が難しいICの集積を成し遂げたことが、最大の成果だ」と強調する。日清紡マイクロデバイス 代表取締役社長の吉岡圭一氏は「今回の成果はアナログICにさらなる進化をもたらし、半導体のヘテロジニアス集積に大きく貢献できるだろう」と語った。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

OKI、超小型「光集積回路チップ」の開発に成功

OKI、超小型「光集積回路チップ」の開発に成功

OKIは、シリコンフォトニクス技術を用いて超小型の「光集積回路チップ」を開発した。この技術を活用すれば、光ファイバーセンサーやレーザー振動計、光バイオセンサーなどのコストダウンが可能となる。 OKI、上越事業所で超高多層PCBの新ライン稼働

OKI、上越事業所で超高多層PCBの新ライン稼働

OKIサーキットテクノロジーで、上越事業所(新潟県上越市)に新設した超高多層PCB(プリント配線板)の回路形成ラインが完成し、本格稼働に入った。新ラインはビアピッチ0.23mmに対応できる。生産能力は従来に比べ1.4倍となった。 縦型GaNパワー半導体のブレークスルーに、新技術の詳細と展望

縦型GaNパワー半導体のブレークスルーに、新技術の詳細と展望

省エネ化/低炭素社会のキーデバイスとして注目されるGaN(窒化ガリウム)を用いたパワー半導体。OKIと信越化学工業のタッグが、その本格的な普及のための課題解決につながる新技術を開発した。同技術の詳細や開発の経緯、今後の展望を聞いた。 センサー回路設計が容易に 利得が最大512倍のPGAを内蔵した汎用AFE

センサー回路設計が容易に 利得が最大512倍のPGAを内蔵した汎用AFE

日清紡マイクロデバイスは、利得が最大512倍というPGAを内蔵した産業機器向け汎用AFE「NA2200」の販売を始めた。動作電源電圧は2.7〜5.5Vで、多くの産業用マイコンと同じ電圧で駆動できる。 「顔で操作」する車載向け非接触UIを展示、日清紡マイクロデバイス

「顔で操作」する車載向け非接触UIを展示、日清紡マイクロデバイス

日清紡マイクロデバイスは「オートモーティブワールド2024」に出展し、非接触の車内UI(ユーザーインタフェース)や衝突防止ソリューションなどの自動車関連技術を紹介した。 「MUSES」シリーズとして初の高音質電源IC

「MUSES」シリーズとして初の高音質電源IC

日清紡マイクロデバイスは、高音質のオーディオ専用デバイス「MUSES」シリーズとして初となる「高音質電源IC」を開発、2022年春よりサンプル出荷を始める。高音質化が進むD-Aコンバーターなどの用途に向ける。