3nm車載SoC「R-Car X5H」用の新技術発表、ルネサス:チップレット構成でASIL-Dに対応

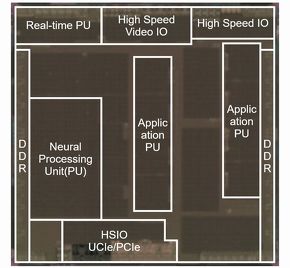

ルネサス エレクトロニクスは、車載向けSoCにおいて高いAI処理性能を実現しつつ、チップレット構成でも機能安全規格に対応できる技術を開発した。これらの技術は3nmプロセス採用の車載マルチドメインECU用SoC「R-Car X5H」のために開発したものだ。同社はR-Car X5Hを、SDV(Software Defined Vehicle)時代に対応する車載用SoCとして提案していく。

高性能化と同時に、高い電力効率と安全性の両立が可能に

ルネサス エレクトロニクスは2026年2月、車載向けSoC(System on Chip)において高いAI処理性能を実現しつつ、チップレット構成でも機能安全規格に対応できる技術を開発したと発表した。これらの技術は同社がサンプル出荷中の車載マルチドメインECU用SoC「R-Car X5H」のために開発したものだ。同社はR-Car X5Hを2027年下期に量産開始する予定で、SDV(Software Defined Vehicle)時代に対応する車載用SoCとして提案していく。

新たに開発したのは、複数のアプリケーションを同時に実現するための高い性能や、チップレットによる柔軟な拡張性に加え、今後の車載用SoCに求められる「電力効率の向上と安全性の両立」を可能にする技術だ。

その1つが、チップレット構成でも車載安全規格「ASIL-D」をサポートできる独自のアーキテクチャだ。標準のダイ間通信規格である「UCIe」の物理アドレス空間に、独自の「RegionID」をマッピングして伝送する方式を開発した。これにより、メモリ管理ユニット(MMU)やリアルタイムコアでの安全なアクセス制御が可能となり、チップレット間でも機能安全規格の要件を満たせるという。しかも、51.2Gバイト/秒という高速伝送を実現した。

もう1つは、高いAI処理能力と車載品質を両立させる技術だ。これまでモジュール化していたクロックパルスジェネレーター(CPG)を分割し、サブモジュール階層にmini-CPG(mCPG)を配置した。この結果、共有するクロック源からの遅延を大幅に削減できた。

ただ、mCPGを多層化するとテストクロックを同期させることが難しくなる。そこで今回、階層型CPGアーキテクチャにテスト回路を統合し、ユーザークロックとテストクロックを単一経路とした。また、テストモードでも上位と下位のmCPGを同一クロック源で同期させる設計とした。これにより一括で調整が可能となった。

さらに、90以上の電源ドメインを用いたパワーゲーティング技術を開発し、電力効率と安全性を両立させた。具体的には、動作状況に応じて数mWから数十Wまで細かな電力制御を可能にした。パワースイッチ(PSW)を「リング型」と「行配置型」に分割。電源投入時にはリング型PSWがラッシュ電流を抑え、行型PSWがドメイン内のインピーダンスを均一化する。これによって、IRドロップを従来に比べ約13%改善した。

また、マスターとチェッカーを独立したパワースイッチとコントローラで制御するDCLS(Dual Core Lock Step)構成とした。これにより、片側故障時でもロックステップ動作による異常検出が可能となった。さらに、各PSWのゲート信号をルーフバック監視することで、異常時のOFF検出を実現した。電圧監視には温度変動に強いデジタル温度モニターを採用し、エージング耐性を1.4mV向上させた。

なお、今回開発した技術の詳細は、米国サンフランシスコで開催された国際固体素子回路学会「ISSCC 2026」(2026年2月15〜19日)で発表した。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

ルネサスがGFと協業、米国での半導体製造を加速

ルネサスがGFと協業、米国での半導体製造を加速

ルネサス エレクトロニクスは、米国における半導体製造を加速させるため、GlobalFoundries(GF)と数十億米ドル規模の製造パートナーシップを結び、戦略的協業を拡大する。 ルネサスがGaN事業拡大、米国EPCとライセンス契約

ルネサスがGaN事業拡大、米国EPCとライセンス契約

ルネサス エレクトロニクスが窒化ガリウム(GaN)パワーデバイス事業を強化する。同社は米国のGaN専業メーカーEPCと包括的なライセンス契約を締結。EPCの低耐圧GaN技術にアクセス可能となり、「AI向け電源アーキテクチャなど高ボリューム市場での機会を拡大する」としている。 IDT買収から7年、ルネサスがタイミング事業をSiTimeに売却

IDT買収から7年、ルネサスがタイミング事業をSiTimeに売却

ルネサス エレクトロニクス(以下、ルネサス)は2026年2月5日、同社のタイミングデバイス事業を米SiTimeに売却すると発表した。売却額は30億米ドル(約4680億円)。ルネサスは売却の理由について「中長期的な成長を見据え、事業の優先順位をこれまで以上に明確にした上で、戦略的な取り組みに最大限の資源を投じることを狙いとしたもの」だとしている。 「SDV開発の促進役」目指すルネサス 最新R-CarのデモをCESで初公開

「SDV開発の促進役」目指すルネサス 最新R-CarのデモをCESで初公開

ルネサス エレクトロニクスは「CES 2026」で、ハイエンドの第5世代車載SoC(System on Chip)「R-Car X5H」を用いたマルチドメインデモを初めて公開した。2025年半ばに出荷を開始したR-Car X5Hのサンプル品を搭載した評価ボードを用いて、先進運転支援システム(ADAS)や車載インフォテインメント(IVI)用のさまざまなソフトウェアが同時に動作する様子を披露した。 ルネサスが第5世代「R-Car」 向け開発プラットフォームを拡充

ルネサスが第5世代「R-Car」 向け開発プラットフォームを拡充

ルネサス エレクトロニクスは、第5世代となるR-Car SoC向け開発プラットフォーム「R-Car Open Access(RoX)」の機能を拡充した。マルチドメイン対応の車載用SoC「R-Car X5H」の評価ボードとソフトウェア群「RoX Whitebox」を新たに用意し、提供を始めた。 常時接続でも低消費電力 Wi-Fi 6/BLE対応マイコン、ルネサス

常時接続でも低消費電力 Wi-Fi 6/BLE対応マイコン、ルネサス

ルネサス エレクトロニクスが、Arm Cortex-Mコア搭載の32ビットマイコン製品群「RAファミリー」の新製品で、スマート家電やIoT用途向けの「RA6シリーズ」を発表した。Wi-Fi 6の2.4GHz/5GHzデュアルバンド対応品と、それに加えてBluetooth Low Energy(LE)にも対応した製品をそろえる。