多ピンと小型・薄型・低コストを両立させるFO-WLPの組み立て技術:福田昭のデバイス通信(217) 2019年度版実装技術ロードマップ(28)(2/2 ページ)

パッケージの組み立てプロセス技術を紹介している。今回は、FO-WLP(Fan Out-Wafer Level Package)の組み立て工程を解説する。

FO-WLPの組み立て工程はSiPに向いている

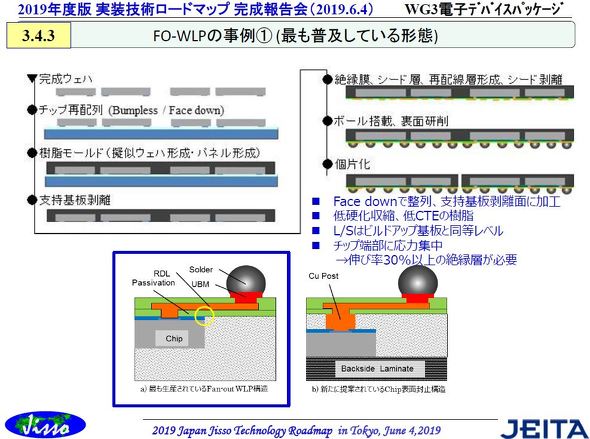

始めは、FO-WLPの中でも最も多く生産されているタイプの組み立てフローを紹介しよう。前回でも説明したようにFO-WLPの組み立て工程では、最初に完成ウエハーを個別のシリコンダイに分割する。それから剥離用テープを表面に貼り付けたガラスウエハー(支持ウエハー)またはガラスパネル(支持パネル)にシリコンダイをフェースダウン(回路面を下にする形態)で搭載する。

ここで重要なのは、支持ウエハーに搭載するシリコンダイは1種類である必要はなく、異なる製造プロセスによる複数のシリコンダイを搭載できることだ。この特徴により、1個のパッケージにシステムを収容するSiP(System in Package)の実現手法としてもFO-WLPは利用されることが少なくない。

組み立てフローに話題を戻そう。シリコンダイを支持ウエハーに搭載した後は、搭載済みのシリコンダイ全体をモールド樹脂で封止する。モールド樹脂の材料には硬化による体積の収縮率が1%以下と低く、熱膨張係数(硬化収縮後)が10ppm/℃前後と小さいことが要求される。それから支持ウエハー(あるいは支持パネル)を剥離する。残されたモールド樹脂封止済みシリコンダイ群でウエハー状のものを「疑似ウエハー」、パネル状のものを「パネル」と呼ぶ。

続いてシリコンダイのフェース(回路面)側に絶縁層を塗布し、銅(Cu)の再配線層を電解めっきによって形成する。なお再配線層の線幅/間隔は20μm/20μm以上である。そしてフラックスを印刷し、はんだボールを搭載する。最後に疑似ウエハーを個別のパッケージに分割する。

ところで、このタイプのFO-WLPはシリコンダイとモールド樹脂の界面(構造図では黄色の円で囲んだ部分)に応力が集中する。この応力は絶縁層と再配線層にクラックを発生させる恐れがある。そこで応力を緩和するため、絶縁層は30%以上と大きく伸びることが求められる。

シリコンダイとモールド樹脂による応力を緩和

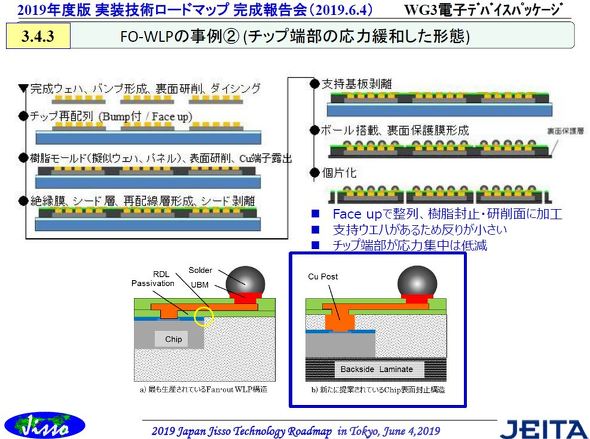

さらに、シリコンダイとモールド樹脂の界面における応力集中の問題を積極的に緩和した構造のFO-WLPが考案され、一部では実用化が始まっている。以下に、応力を緩和したFO-WLPの組み立てフローを説明しよう。

まず、完成ウエハーの入出力パッドにCuバンプを搭載し、裏面を研削する。続いて個別のシリコンダイを切り出す。そして剥離用テープを表面に貼り付けたガラスウエハー(支持ウエハー)またはガラスパネル(支持パネル)に、シリコンダイをフェースアップ(回路面を上にする形態)で搭載する。続いてシリコンダイを覆うようにモールド樹脂で封止し、表面(フェース側)を研削してCuバンプを露出させる。

次に、絶縁層と再配線層を形成する。なお、この構造では支持ウエハーがあるので、全体が反りにくい。絶縁層と再配線層を形成してから、支持ウエハーを剥離する。続いてシリコンダイの回路面にフラックスを印刷し、はんだボールを搭載する。シリコンダイの裏面には保護膜(樹脂フィルム)を貼る。それから個別のパッケージに分割する。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

小型・薄型・低コストのパッケージを実現する組み立て技術

小型・薄型・低コストのパッケージを実現する組み立て技術

今回から、パッケージの組み立てプロセスの技術動向を紹介する。まずは、QFN、BGA、WL-CSP、FO-WLPの組み立て工程を取り上げる。 5Gの移動通信システムを支えるミリ波のパッケージ技術

5Gの移動通信システムを支えるミリ波のパッケージ技術

今回は、第5世代(5G)の移動通信システムに向けたミリ波対応のSiP(System in Package)技術を紹介する。ミリ波帯向けでは、アンテナとFEM(Front End Module)を積層した「AiP(Antenna in Package)というSiPの実用化が始まっている。 1個のパッケージでシステムを実現するSiP

1個のパッケージでシステムを実現するSiP

今回は、SiP(System in Package)を実現する幾つかの手法のうち、2.X次元(2.XD)の実装技術を解説する。ここでカギとなるのは、インタポーザだ。 SCREEN、洗浄装置や膜厚測定装置で処理能力向上

SCREEN、洗浄装置や膜厚測定装置で処理能力向上

SCREENセミコンダクターソリューションズは、「SEMICON Japan 2019」で、スループットを向上させた枚葉式洗浄装置「SU-3300」や光干渉式膜厚測定装置「VM-2500」などのパネル展示を行った。 2019年Q3の半導体売上高ランキング、ソニーが9位に

2019年Q3の半導体売上高ランキング、ソニーが9位に

2019年第3四半期の世界半導体売上高は、メモリ市場は成長の兆しを見せているが、引き続き下落傾向にある。今回の売上高ランキングでは、Intelが引き続き第1を維持した他、ソニーセミコンダクタソリューションズが、今回初めてトップ10入りを果たすという偉業を成し遂げた。 「世界の半導体業界を支える日本」を強調したい SEMI

「世界の半導体業界を支える日本」を強調したい SEMI

SEMIジャパンは2019年12月10日、都内で記者発表会を開催し、12月11〜13日にかけて開催される「SEMICON Japan 2019」(東京ビッグサイト)のハイライトと、2020年の半導体市場予測について説明した。