国際学会IEDMの記者室にVLSIシンポジウムの実行委員会が再び乱入:福田昭のデバイス通信(220)(2/2 ページ)

2019年12月に開催された「IEDM 2019」の記者室に、国際学会VLSIシンポジウムの実行委員会が“乱入”し、シンポジウムの開催概要を説明した。今回は、そのミニ説明会の内容を紹介する。

4件の基調講演の中で3件の講演者が決定済み

メインイベントの技術講演会では、17日の朝と18日の朝に2件ずつの基調講演(プレナリー講演)が実施される。12月9日の時点では、合計4件の中で3件の講演者が決定していた。Intelの最高技術責任者(CTO)をつとめるMichael Mayberry氏、NTTドコモの執行役員で5Gイノベーション推進室長をつとめる中村武宏氏、キオクシアでSSD応用技術技師長をつとめる大島成夫氏である。あと1人は、早ければIEDMの開催期間中に決まるとPalacios氏は述べていた。

投稿の締め切りは2020年2月10日、残りあと約1カ月

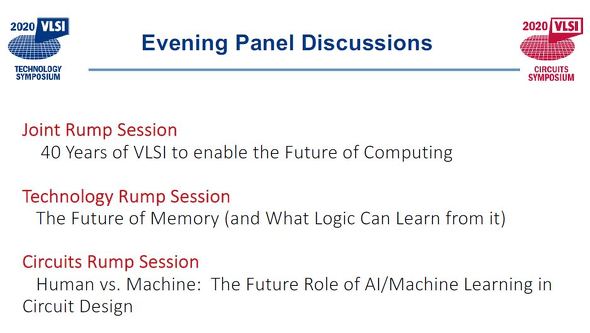

技術講演会以外のイベントについても説明があった。夜間に実施されるパネル討論会(パネルディスカッション)は、3件を予定する。

1件は技術シンポジウムと回路シンポジウムの共同パネル討論会で、6月15日の夜に実施される。テーマは「コンピューティングの未来を実現するVLSIの40年」である。

残りの2件は技術シンポジウムのパネル討論会と回路シンポジウムのパネル討論会で、いずれも6月16日の夜を予定する。前者のテーマは「メモリの将来(そこからロジックが学べることは何か)」、後者のテーマは「人間対機械:回路設計におけるAI/機械学習の役割」である。

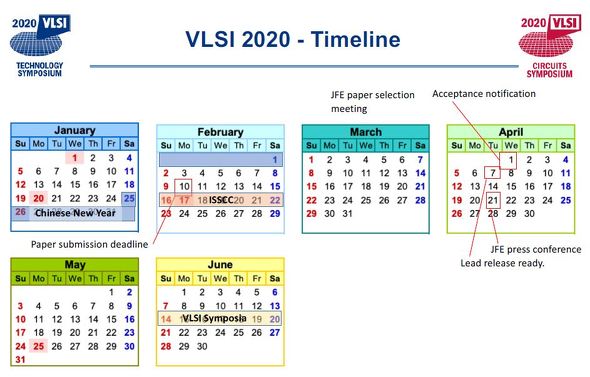

2020年のVLSIシンポジウムで発表される研究成果は、現時点では決まっていない。投稿論文の締め切りは2020年2月10日である。投稿論文が採択されたかどうかが投稿者に通知されるのは、2020年4月1日を予定する。同じ4月21日には、報道機関向けの説明会が開催される。来年(2020年)の4月を楽しみに待ちたい。

⇒「福田昭のデバイス通信」連載バックナンバー一覧

《次の記事を読む》

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

部品内蔵基板の組み立て技術

部品内蔵基板の組み立て技術

今回は、部品内蔵基板の組み立て工程を紹介する。半導体チップをフェースダウン(回路面を下にした状態)で基板に搭載する技術、フェースアップ(回路面を上にした状態)で基板に搭載する技術、微細な配線を形成できる技術の3つについて解説したい。 微細配線が可能なFO-WLPの組み立て技術

微細配線が可能なFO-WLPの組み立て技術

前回に続き、FO-WLP(Fan Out-Wafer Level Package)の組み立て工程を解説する。今回は、微細配線を形成可能なFO-WLPを取り上げる。 多ピンと小型・薄型・低コストを両立させるFO-WLPの組み立て技術

多ピンと小型・薄型・低コストを両立させるFO-WLPの組み立て技術

パッケージの組み立てプロセス技術を紹介している。今回は、FO-WLP(Fan Out-Wafer Level Package)の組み立て工程を解説する。 3D NANDフラッシュメモリの断面構造と製造工程

3D NANDフラッシュメモリの断面構造と製造工程

2018年5月に開催された国際会議「IMW」で行われたセミナー「3D NAND技術とそのスケーリングに関する材料とプロセス、製造装置の展望」の概要をシリーズで紹介している。今回は、3D NANDフラッシュメモリの断面構造と、メモリセルアレイの製造工程を解説しよう。 2D NANDと3D NANDのスケーリング(高密度化)手法

2D NANDと3D NANDのスケーリング(高密度化)手法

今回は、2D NANDフラッシュ(プレーナーNANDフラッシュ)と3D NANDフラッシュのスケーリング(高密度化)手法の違いについて解説する。 3D NANDフラッシュ製造のカギとなるプロセス技術

3D NANDフラッシュ製造のカギとなるプロセス技術

今回は、3D NANDフラッシュメモリの製造プロセスにおける重要な技術(キープロセス)について解説する。