東芝、高周波IC向け最新SOIプロセス技術を開発:8GHzで最小雑音指数0.48dBを達成

東芝デバイス&ストレージは、5G(第5世代移動通信)対応スマートフォンなどに向けた高周波スイッチ/低雑音アンプ(LNA)ICを製造するためのSOI(Silicon On Insulator)プロセス技術「TaRF11」を新たに開発した。

LNA、高周波スイッチ、制御回路をワンチップに集積

東芝デバイス&ストレージは2020年2月、5G(第5世代移動通信)対応スマートフォンなどに向けた高周波スイッチ/低雑音アンプ(LNA)ICを製造するためのSOI(Silicon On Insulator)プロセス技術「TaRF11」を新たに開発したと発表した。

スマートフォンやWi-Fiなどの無線機器は、高速・大容量通信に向けて無線帯域が高周波化している。これに伴い、アンテナと受信回路間の信号ロスが増えている。こうした課題を解決するために、LNAの特性向上などが求められているという。

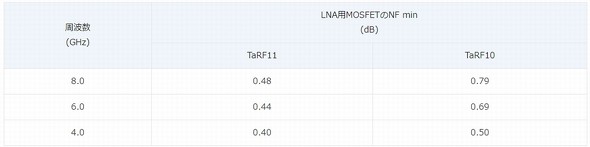

同社は、高周波半導体向けに独自開発したSOI-CMOSフロントエンドプロセス「TarfSOI」を用い、高周波デバイスを製造してきた。TaRF11は、既存のプロセス技術「TaRF10」に比べて特性を改善した。

例えば、TaRF11を用いて製造したLNA用MOSFETは、周波数8GHzにおける最小雑音指数(NFmin)が0.48dBである。TaRF10を用いた製品に比べると約0.3dBも改善している。また、これまでのように、LNAと高周波スイッチおよび、制御回路をワンチップに集積することができる。なお、製造はグループ会社「ジャパンセミコンダクター」で生産する。

同社は引き続き、TarfSOIプロセスの高性能化に取り組む。その上で、7G〜10GHz帯のUWB(超広帯域無線システム)などに向けた高周波スイッチ/LNA ICなども開発していく計画である。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

東芝、角度直接検出型のRIGモジュールを開発

東芝、角度直接検出型のRIGモジュールを開発

東芝は、回転する角度を直接検出できる小型のジャイロセンサー(RIG:Rate Integrating Gyroscope)モジュールを開発した。 東芝メモリ、新型リムーバブルメモリデバイス開発

東芝メモリ、新型リムーバブルメモリデバイス開発

東芝メモリは、ウルトラモバイルPCなどに向けた、新しいリムーバブルPCIe/NVMeメモリデバイス「XFMEXPRESS」を開発した。 東芝メモリ、「キオクシア」(Kioxia)に社名変更へ

東芝メモリ、「キオクシア」(Kioxia)に社名変更へ

東芝メモリホールディングスは2019年7月18日、2019年10月1日付で社名を「キオクシアホールディングス」に変更すると発表した。同社の子会社である東芝メモリも同様に、キオクシアに社名変更する。 東芝、高感度のフィルム型有機光センサーを開発

東芝、高感度のフィルム型有機光センサーを開発

東芝は、有機半導体を用いた高感度のフィルム型光センサーを開発した。開発した光センサーと放射線によって発光するシンチレーターを組み合わせ、放射線のパルス検出に初めて成功した。 東芝、ミリ波応用の電波イメージング技術を開発

東芝、ミリ波応用の電波イメージング技術を開発

東芝は、ミリ波レーダーを照射して、衣服の下に隠し持った危険物を可視化できる「電波イメージング技術」を開発した。テロ対策など警備システムの用途に向ける。 複数信号の双方向通信を実現する絶縁ICなど開発、東芝

複数信号の双方向通信を実現する絶縁ICなど開発、東芝

東芝は2020年2月21日、3つの信号の双方向通信と100mW以上の電力電送が可能な「双方向多重伝送IC」および、データセンターのサーバ用電源システムなどに搭載できる「高速絶縁計測IC」を開発したと発表した。いずれも2022年度以降のサンプル提供を目指している。