EUVāŖā\āOāēātāBéĢŌŖ«éĘéķÄ®ī╚ægÉDē╗āŖā\āOāēātāBüFĢ¤ōcÅ║é╠āfāoāCāXÆ╩ÉMüi293üj Intelé¬īĻéķāIāōā`ābāvé╠æĮæwözɳŗZÅpüi14üjüi2/2 āyü[āWüj

ŹĪē±é═üAÄ®ī╚ægÉDē╗āŖā\āOāēātāBé¬EUVüiŗ╔Æ[ÄćŖOɳüjāŖā\āOāēātāBé╠ÄŃō_éĢŌŖ«éĘéķŗZÅpé┼éĀéķé▒éŲéÉÓ¢ŠéĘéķüB

özɳĢØéŲözɳÆ[Ģöé╠é╬éńé┬é½éīĖéńéĘ

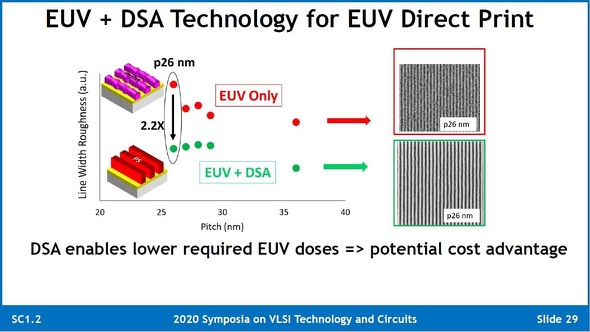

ü@é╗é▒é┼EUVāŖā\āOāēātāBé┼āīāWāXāgé╔ĢĮŹsözɳīQé╠āpā^ü[āōéī`ɼéĄéĮéĀéŲé┼üAāīāWāXāgéözɳé┼é═é╚éŁüADSAāŖā\āOāēātāBé╠ē║Ænæwé╠āpā^ü[āōī`ɼé╔Ägéżé▒éŲéŹlé”éķüBé▒éżéĘéķéŲüAŚßé”é╬āsābā`é¬26nmé╠ĢĮŹsözɳāpā^ü[āōéī`ɼéĄéĮéŲé½é╔üAözɳĢØé╠é╬éńé┬é½üiLWRüjé¬2.2Ģ¬é╠1üi45üōüjé╔īĖéńé╣éķéŲéĘéķüB

EUVāŖā\āOāēātāBé╔DSAāŖā\āOāēātāBéægé▌ŹćéĒé╣éķé▒éŲé┼üAözɳĢØé╠é╬éńé┬é½üiLWRüjé45üōüi2.2Ģ¬é╠1üjé╔ÆßīĖüiözɳāsābā`é═26nmüjüBŹČé═özɳāsābā`éŲLWRé╠ŖųīWüBēEé═26nmāsābā`é╠ĢĮŹsÆ╝ɳīQéī`ɼéĄéĮāpā^ü[āōé╠ŖŽÄ@æ£üBÅoōTüFIntelüiāNāŖābāNé┼ŖgæÕüj

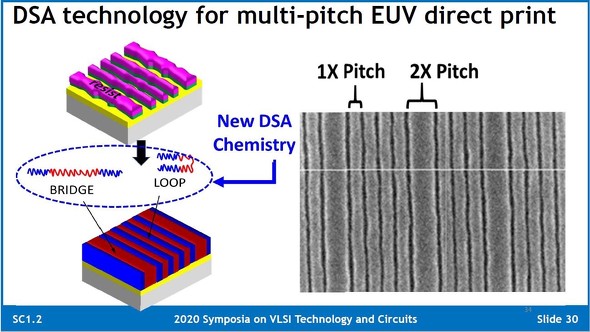

ü@é▄éĮDSAāŖā\āOāēātāBé═EUVāŖā\āOāēātāBéŲægé▌ŹćéĒé╣éķé▒éŲé┼üAŖŅ¢{āsābā`üiü~1āsābā`üjéŲ2ö{āsābā`üiü~2āsābā`üjé╠ĢĮŹsözɳāpā^ü[āōéłĻŖćéĄé─ŹņéĻéķéŲéĄéĮüBŚßé”é╬PMMA-b-PS-b-PMMAéŲéóé┴éĮŗżÅdŹćŹéĢ¬ÄqéÄgéżüBÆåēøé╠PSĢöé¬ÆĘéŁüAŚ╝Æ[é╠PMMAĢöé═PSĢöé╠ö╝Ģ¬éŲÆZéóüBÆ╝ɳžé╔ÉLéčéĮŗżÅdŹćŹéĢ¬Äqé═2ö{āsābā`üAÉ^é±Æåé┼É▄éĶĢįéĄéĮŗżÅdŹćŹéĢ¬Äqé═ŖŅ¢{āsābā`é╠ŚvæféŲé╚éķüB

ŖŅ¢{āsābā`üiü~1āsābā`üjéŲ2ö{āsābā`üiü~2āsābā`üjé╠ĢĮŹsözɳāpā^ü[āōéEUVéŲDSAé╠ægé▌ŹćéĒé╣é┼ī`ɼéĘéķüBŹČé═ī┤ŚØÉ}üBÆ╝ɳžé╔ÉLéčéĮŗżÅdŹćŹéĢ¬Äqé═2ö{āsābā`üAÉ^é±Æåé┼É▄éĶĢįéĄéĮŗżÅdŹćŹéĢ¬Äqé═ŖŅ¢{āsābā`é╠āpā^ü[āōéŲé╚éķüBēEé═ÄÄŹņéĄéĮāpā^ü[āōé╠ŖŽÄ@æ£üBÅoōTüFIntelüiāNāŖābāNé┼ŖgæÕüj

üiĤē±é╔æ▒éŁüj

ü╦üuĢ¤ōcÅ║é╠āfāoāCāXÆ╩ÉMüvśAŹ┌āoābāNāiāōāoü[łĻŚŚ

Copyright © ITmedia, Inc. All Rights Reserved.

ŖųśAŗLÄ¢

śIī§ŗZÅpé╠ö„Źūē╗ī└ŖEéō╦öjéĘéķÄ®ī╚ægÉDē╗ŗZÅp

śIī§ŗZÅpé╠ö„Źūē╗ī└ŖEéō╦öjéĘéķÄ®ī╚ægÉDē╗ŗZÅp

ŹĪē±é®éńüAArFētÉZŗZÅpéŌEUVüiŗ╔Æ[ÄćŖOɳüjŗZÅpé╚éŪé╠śIī§ŗZÅpé╠ö„Źūē╗ī└ŖEéÆ┤é”éķüAéĀéķéóé═é▒éĻéńé╠śIī§ŗZÅpéēä¢Įé│é╣éķĤÉóæŃé╠āŖā\āOāēātāBŗZÅpüuÄ®ī╚ægÉDē╗āŖā\āOāēātāBüvéé▓ÅąēŅéĘéķüB æĮæwözɳé╠ɽö\éī³ÅŃé│é╣éķāGāAāMāāābāvéŲ2Ĥī│Ź▐Ś┐

æĮæwözɳé╠ɽö\éī³ÅŃé│é╣éķāGāAāMāāābāvéŲ2Ĥī│Ź▐Ś┐

ŹĪē±é═üAæĮæwözɳé╠ŚeŚ╩éē║é░éķŚvæfŗZÅpüuāGāAāMāāābāvüvéŲüAæĮæwözɳé╠Æ’ŹRéē║é░éķŚvæfŗZÅpüu2Ĥī│üi2DüjŹ▐Ś┐üvé╔é┬éóé─ēÉÓéĘéķüB æĮæwözɳé╠āAāXāyāNāgöõüiARüjéŹéé▀éķ2é┬é╠ŚvæfŗZÅp

æĮæwözɳé╠āAāXāyāNāgöõüiARüjéŹéé▀éķ2é┬é╠ŚvæfŗZÅp

özɳé╠āAāXāyāNāgöõüiARüjéŹéé▀éķüA2é┬é╠ŚvæfŗZÅpé╔é┬éóé─ēÉÓéĘéķüB æĮæwözɳé╠āAāXāyāNāgöõüiARüjéŲÆ’ŹRé©éµéčŚeŚ╩é╠ŖųīW

æĮæwözɳé╠āAāXāyāNāgöõüiARüjéŲÆ’ŹRé©éµéčŚeŚ╩é╠ŖųīW

ŹĪē±é═üAözɳé╠āAāXāyāNāgöõüiARüjéŲözɳƒŹRé©éµéčözɳŚeŚ╩é╠ŖųīWéŖTÉÓéĘéķüB ō║üiCuüjözɳé╠ö„Źūē╗éŲÆ’ŹRÆlé╠æØæÕ

ō║üiCuüjözɳé╠ö„Źūē╗éŲÆ’ŹRÆlé╠æØæÕ

ł°é½æ▒é½üAāIāōā`ābāvé╠æĮæwözɳŗZÅpé╔ŖųéĘéķIntelé╠ŹuēēōÓŚeéÅąēŅéĘéķüBŹĪē±é═üAō║özɳé╠ÉĪ¢@éŲōdŗCÆ’ŹRé╠ŖųīWéÉÓ¢ŠéĘéķüB āĆü[āAæźé╠ł█ÄØé╔ŹvīŻéĘéķözɳŗZÅp

āĆü[āAæźé╠ł█ÄØé╔ŹvīŻéĘéķözɳŗZÅp

üuVLSIāVāōā|āWāEāĆüvé®éńüAāIāōā`ābāvé╠æĮæwözɳŗZÅpé╔ŖųéĘéķIntelé╠ŹuēēōÓŚeéÅąēŅéĘéķāVāŖü[āYüBŽŚłé╠özɳŗZÅpé╔é═üAāTāuāgāēāNāeāBāu¢@éŌÆߌUōdŚ”ÉŌēÅŹ▐Ś┐é╚éŪé╔Ŗ·æęé¬é®é®é┴é─éóéķüB