ビアの位置ずれ不良を救う選択成長技術:福田昭のデバイス通信(294) Intelが語るオンチップの多層配線技術(15)

今回から、基板表面の一部だけを選んで薄膜を堆積(成長)させる技術(「選択デポジション(selective deposition)」あるいは「選択成長(selective growth)」)と、選択成長技術がビアの位置ずれ不良に応用できることを説明する。

基板表面の一部だけに薄膜を選択的に成長させる

半導体のデバイス技術と回路技術に関する国際学会「VLSIシンポジウム」では、「ショートコース(Short Course)」と呼ぶ技術講座を開催してきた。2020年6月に開催されたVLSIシンポジウムのショートコースは、3つの共通テーマによる1日がかりの技術講座が設けられていた。その中で「SC1:Future of Scaling for Logic and Memory(ロジックとメモリのスケーリングの将来)」を共通テーマとする講演、「On-Die Interconnect Challenges and Opportunities for Future Technology Nodes(将来の技術ノードに向けたオンダイ相互接続の課題と機会)」が非常に興味深かった。そこで講演の概要を本コラムの第280回からシリーズでお届けしている。講演者はIntelのMauro J. Kobrinsky氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

本シリーズの第12回から、ArF液浸技術やEUV技術などの露光技術の微細化限界を超える、あるいはこれらの露光技術を延命させる次世代のリソグラフィ技術の講演部分を紹介している。第12回と第13回、第14回(前回)は、「自己組織化リソグラフィ(DSAリソグラフィ)」技術の概要と同技術による微細な配線パターンの試作例、DSAリソグラフィがEUVリソグラフィを補完できることをご報告した。

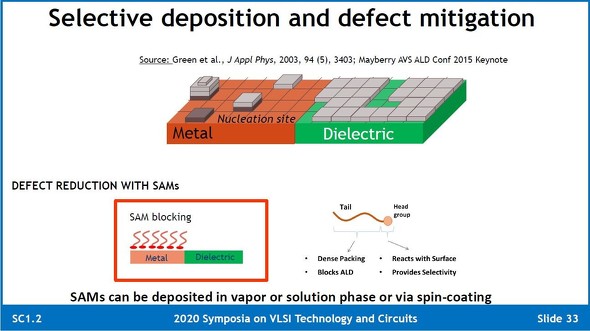

今回からは、基板表面の一部だけを選んで薄膜を堆積(成長)させる技術(「選択デポジション(selective deposition)(選択デポ)」あるいは「選択成長(selective growth)」)と、選択成長技術がビアの位置ずれ不良に応用できることを説明する。特にここでは、「自己組織化単分子(SAM:Self-Assembled Monolayer)膜」をマスクとして利用する選択成長技術について述べる。広義のボトムアップ・リソグラフィとも言える技術である。

自己組織化単分子(SAM)膜を利用した選択成長

「自己組織化単分子(SAM:Self-Assembled Monolayer)膜」とは、有機分子が基板の表面に規則的に並んで結合あるいは付着して形成する単分子層の薄膜を指す。SAM膜は、厚みが均一(単分子の長さ)という特徴を備える。

SAM膜を形成する有機分子(SAM分子)は通常、「ヘッドグループ(head group)」と呼ぶ先端部分と「テイルグループ(tail group)」と呼ぶ末端部分に分けられる。ヘッドグループは基板表面と反応して結合あるいは吸着する。テイルグループはSAM膜表面の性質を決める。ここで重要なのは、あるSAM分子のヘッドグループと別のSAM分子のテイルグループは反応せず、吸着しないことである。この性質により、SAM分子が基板表面で重なることなく、単分子の状態で基板表面を覆うと自動的にSAM分子の吸着反応が停止する。すなわち通常の成膜プロセスと違い、膜厚を制御する必要がない。

選択成長における欠陥の低減。絶縁膜あるいは金属膜の表面に自己組織化単分子(SAM:Self-Assembled Monolayer)膜を選択的に付着させる。SAM分子の先端(ヘッドグループ)が、絶縁膜あるいは金属膜だけと反応してSAM膜を形成する。下左は、金属膜だけにSAM膜が選択的に堆積した例。SAM膜をマスクとして、誘電膜表面だけに所望の薄膜を選択的に成長させる。出典:Intel(クリックで拡大)

ビアの位置ずれが短絡不良を起こす

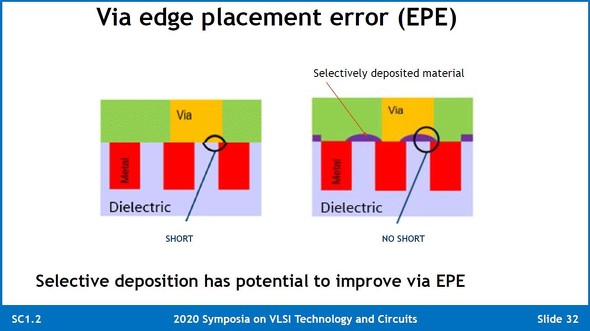

SAM膜を使った選択成長技術は、多層配線構造におけるビアの位置ずれによって生じる短絡不良を救える可能性がある。ビアの下層の配線層は、配線幅が配線間隔(絶縁膜の幅)に比べて広いことが多い。そしてビアの直径は、下層の配線幅に比べると長いことが少なくない。

ここでビアの中心が配線の中心からずれると、ビアの端が隣接する配線と接して短絡してしまう。ArF液浸リソグラフィではレイアウト・パターンと実際のレジスト露光パターンにずれが生じる、「EPE(Edge Placement Error)」が大きな課題となっている(参考記事:「ニコンが展望する10nm以下のリソグラフィ技術(前編))。EPEによってビアの位置がずれ、短絡不良を生じる恐れが少なくない。

レイアウト・パターンと実際のレジスト露光パターンにずれが生じる「EPE(Edge Placement Error)」の影響例。左は通常の多層配線構造。ビアの位置ずれによって隣接配線との短絡不良が生じている。右は選択成長技術によって絶縁膜を成長させて配線層の上面を狭くした構造。ビアの位置がずれても短絡不良は起きない。出典:Intel(クリックで拡大)

この不良を救済する手法の一つが、配線間絶縁膜の表面だけに選択的に絶縁膜を成長させ、配線層の上面を狭くすることだ。EPEによってビアがずれても、選択成長させた絶縁膜が隣接する配線との短絡を防ぐ。この選択成長にSAM膜を利用する。そのプロセスと試作例は、本シリーズの次回で説明する。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

露光技術の微細化限界を突破する自己組織化技術

露光技術の微細化限界を突破する自己組織化技術

今回から、ArF液浸技術やEUV(極端紫外線)技術などの露光技術の微細化限界を超える、あるいはこれらの露光技術を延命させる次世代のリソグラフィ技術「自己組織化リソグラフィ」をご紹介する。 多層配線の性能を向上させるエアギャップと2次元材料

多層配線の性能を向上させるエアギャップと2次元材料

今回は、多層配線の容量を下げる要素技術「エアギャップ」と、多層配線の抵抗を下げる要素技術「2次元(2D)材料」について解説する。 多層配線のアスペクト比(AR)を高める2つの要素技術

多層配線のアスペクト比(AR)を高める2つの要素技術

配線のアスペクト比(AR)を高める、2つの要素技術について解説する。 多層配線のアスペクト比(AR)と抵抗および容量の関係

多層配線のアスペクト比(AR)と抵抗および容量の関係

今回は、配線のアスペクト比(AR)と配線抵抗および配線容量の関係を概説する。 銅(Cu)配線の微細化と抵抗値の増大

銅(Cu)配線の微細化と抵抗値の増大

引き続き、オンチップの多層配線技術に関するIntelの講演内容を紹介する。今回は、銅配線の寸法と電気抵抗の関係を説明する。 ムーア則の維持に貢献する配線技術

ムーア則の維持に貢献する配線技術

「VLSIシンポジウム」から、オンチップの多層配線技術に関するIntelの講演内容を紹介するシリーズ。将来の配線技術には、サブトラクティブ法や低誘電率絶縁材料などに期待がかかっている。