ŹéŚZō_ŗÓæ«é╠æĮæwözɳŗZÅpé¬2nmł╚Ź~é╠CMOSéÄ└ī╗üFĢ¤ōcÅ║é╠āfāoāCāXÆ╩ÉMüi319üj imecé¬īĻéķ3nmł╚Ź~é╠CMOSŗZÅpüi22üj

æOē±é®éńüuĤÉóæŃé╠æĮæwözɳüiBEOLüjŗZÅpüvé╠ŹuēēōÓŚeéÅąēŅéĄé─éóéķüBŹĪē±é═üAō║üiCuüjł╚ŖOé╠özɳŗZÅpéō▒ō³éĘéķŹ█é╠ī¾ĢŌéŲé╚éķŹéŚZō_ŗÓæ«é╔é┬éóé─ēÉÓéĘéķüB

21nmāsābā`é¬ō║özɳé╠ī└ŖEō_éŲŚ\æ¬

ü@ö╝ō▒æ╠é╠āfāoāCāXŗZÅpéŲāvāŹāZāXŗZÅpé╔ŖųéĘéķÉóŖEŹ┼æÕé╠ŹæŹ█Ŗwē’üuIEDMüiInternational Electron Devices Meetingüjüvé═üAüuā`āģü[āgāŖāAāŗüiTutorialsüjüvéŲī─éįŗZÅpŹuŹ└é¢{ē’ŗcüiŗZÅpŹuēēē’üjéŲé═Ģ╩é╔üAāvāīāCāxāōāgéŲéĄé─ŖJŹ├éĄé─é½éĮüB2020öN12īÄé╔ŖJŹ├é│éĻéĮIEDMüiCovid-19é╠ÉóŖEōIé╚Ś¼Źsé╔éµé┴é─āoü[ā`āāāŗāCāxāōāgéŲéĄé─ŖJŹ├üjüAÆ╩Å╠üuIEDM2020üvé┼é═üAŹćīvé┼6¢{é╠ā`āģü[āgāŖāAāŗŹuēēé¬Ä└Ä{é│éĻéĮüBé╗é╠Æåé┼üuInnovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materialsüiCMOSé3nmł╚ē║é╔ö„Źūē╗éĘéķŚvæfŗZÅp-āfāoāCāXāAü[āLāeāNā`āāéŲŖ±ÉČæfÄqüAŹ▐Ś┐üjüvé¬ö±ÅĒé╔ŗ╗¢ĪÉ[é®é┴éĮüBŹuēēÄęé═īżŗåŖJöŁŗ@Ŗųé╠imecé┼Technology Solutions and EnablementÆSō¢āoāCāXāvāīāWāfāōāgéé┬éŲé▀éķMyungü]Hee NaÄüé┼éĀéķüB

ü@é╗é▒é┼¢{ŹuŹ└é╠ŖTŚvé¢{āRāēāĆé╠æµ298ē±é®éńüAāVāŖü[āYé┼é©ō═é»éĄé─éóéķüBé╚é©Źuēēé╠ōÓŚeéŠé»é┼é═ÉÓ¢Šé¬ĢsÅ\Ģ¬é╚éŲé▒éļé¬éĀéķé╠é┼üA¢{āVāŖü[āYé┼é═ōŪÄęé╠ŚØēéÅĢé»éķéĮé▀é╔üAŹuēēé╠ōÓŚeéōKŗXüAĢŌæ½éĄé─éóéķüBéĀéńé®éČé▀é▓Ś╣Å│é│éĻéĮéóüB

ā`āģü[āgāŖāAāŗŹuēēüuInnovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materialsüiCMOSé3nmł╚ē║é╔ö„Źūē╗éĘéķŚvæfŗZÅp-āfāoāCāXāAü[āLāeāNā`āāéŲŖ±ÉČæfÄqüAŹ▐Ś┐üjüvé╠āAāEāgāēāCāōüBŹuēēāXāēāCāhæSæ╠é®éńĢMÄę鬏ņɼéĄéĮéÓé╠üBæOē±é®éńüAüuĤÉóæŃé╠æĮæwözɳüiBEOLüjŗZÅpüvé╠Źuēēāpü[āgéÅąēŅéĄé─éóéķüiāNāŖābāNé┼ŖgæÕüj

ü@æOē±é®éńüA5öį¢┌é╠āpü[āgé┼éĀéķüuĤÉóæŃé╠æĮæwözɳüiBEOLüjŗZÅpüvé╠ŹuēēōÓŚeéÅąēŅéĄé─éóéķüBÄÕæĶé═üA3nmł╚Ź~é╠ŗZÅpÉóæŃüiŗZÅpāmü[āhüjéÆSéżæĮæwözɳŗZÅpé┼éĀéķüB

ü@æOē±é┼ÅqéūéĮéµéżé╔üA3nmł╚Ź~é╠CMOSāŹāWābāNé┼é═ō║üiCuüjé╠āfāģāAāŗā_ā}āVāōŗZÅpé╔éµéķæĮæwözɳé¬ī└ŖEé╔ŗ▀é├éŁüBimecé═ī└ŖEéŲé╚éķözɳāsābā`é21nméŲŚ\æ¬éĄé─é©éĶüA21nmł╚Ź~é═ō║üiCuüjł╚ŖOé╠özɳŗZÅpéō▒ō³éĄé╚é»éĻé╬é╚éńé╚éóüBé▒é╠éµéżé╔Źlé”éķüB

özɳæwŖįé╠ārāAéŹéŚZō_ŗÓæ«é┼¢äé▀éķ

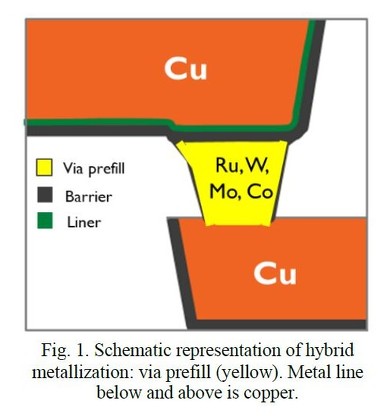

ü@æĮæwözɳé╠ō▒æ╠ĢöĢ¬é═üAĢĮŹsé╚Æ╝ɳözɳīQé╠æwüiözɳæwüjéŲæwŖįéīŗéįārāAōdŗ╔é┼Ź\ɼé│éĻéķüBÄné▀é╔ö„Źūē╗é╠ī└ŖE鬌łéķé╠é═üAārāAōdŗ╔é┼éĀéķüBé╗é▒é┼ārāAōdŗ╔éō║üiCuüjé┼é═é╚éŁüAŹéŚZō_ŗÓæ«é╠ā^āōāOāXāeāōüiWüjéŌāéāŖāuāfāōüiMoüjüAāRāoāŗāgüiCoüjüAāŗāeājāEāĆüiRuüjé╚éŪé╔ĢŽŹXéĘéķüB

özɳæwéō║üiCuüjüAārāAōdŗ╔éŹéŚZō_ŗÓæ«é┼ī`ɼéĘéķæĮæwözɳé╠Æf¢╩Ź\æóÉ}üBÅoōTüFimecüiIEDM 2020é╠öŁĢ\ś_ĢČüuInflection points in interconnect research and trends for 2nm and beyond in order to solve the RC bottlenecküvüiś_ĢČöįŹå32.2üjüj üiāNāŖābāNé┼ŖgæÕüj

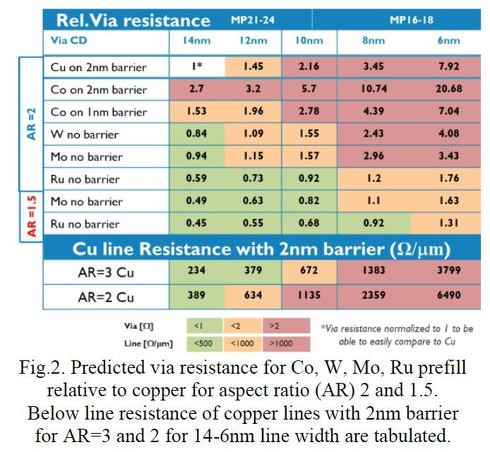

ārāAōdŗ╔é╠ö„Źūē╗é╔éµéķÆ’ŹRÆlé╠ĢŽē╗éō║éŲŹéŚZō_ŗÓæ«é┼öõŖrüiīvÄZÆlüjüBæÕé½é│14nmé╠ārāAéāAāXāyāNāgöõüiARüj2é╠ō║üiCuüjüiāoāŖāAæwé╠ī·é▌é═2nmüjé┼¢äé▀éĮéŲé½é╠Æ’ŹRÆléŖŅÅĆüi1üjéŲéĄéĮæŖæ╬Ælé┼éĀéķüBÅoōTüFimecüiIEDM 2020é╠öŁĢ\ś_ĢČüuInflection points in interconnect research and trends for 2nm and beyond in order to solve the RC bottlenecküvüiś_ĢČöįŹå32.2üjüj üiāNāŖābāNé┼ŖgæÕüj

ü@æÕé½é│é¬14nmé╠ārāAüiözɳāsābā`21nmü`24nmé╠æĮæwözɳŹ\æóé╔æŖō¢üjéī·é▌2nmé╠āoāŖāAæwéŲō║üiCuüjé┼¢äé▀éĮÅĻŹćé╠ārāAÆ’ŹRüiāAāXāyāNāgöõüiARüjé═2üjéŖŅÅĆüi1.00üjéŲéĘéķüBārāAé╠æÕé½é│é¬10nmé╔ŹūéŁé╚éķéŲüAÆ’ŹRÆlüiæŖæ╬Ælüjé═2.16éŲŖŅÅĆé╠2ö{éÆ┤é”éķüB

ü@łĻĢ¹é┼ŖŅÅĆéŲō»éČ14nmé╠ārāAüiARé═2üjé┼āoāŖāAæwé╠é╚éóā^āōāOāXāeāōüiWüjé═0.84üAāoāŖāAæwé╠é╚éóāéāŖāuāfāōüiMoüjé═0.94üAāoāŖāAæwé╠é╚éóāŗāeājāEāĆüiRuüjé═0.59é╔ārāAÆ’ŹRüiæŖæ╬Ælüjé¬ē║é¬éķüB

ü@é▄éĮō║üiCuüjözɳé╠Æ’ŹRÆlüiÆPł╩ÆĘō¢éĮéĶüjé═üAözɳĢØé¬14nmé┼āAāXāyāNāgöõüiARüjé¬3é╠éŲé½é╔234āČ/ā╩müAARé¬2é╠éŲé½é╔389āČ/ā╩méŲé╚éķüBözɳĢØé10nmé╔ŹūéŁéĘéķéŲüAARé¬3é╠éŲé½é╔672āČ/ā╩müAARé¬2é╠éŲé½é╔1135āČ/ā╩méŲÆ’ŹRÆlé═¢±2.9ö{é╔æØē┴éĘéķüB

āŗāeājāEāĆüiRuüjé¬Å½Śłé╠æĮæwözɳé┼é═ŚL¢]

ü@é▒éĻéńé╠ÉäÆĶé®éńüAimecé═ŽŚłŚL¢]é╚ŗÓæ«éāŗāeājāEāĆüiRuüjéŲŹlé”é─éóéķüBÆ’ŹRŚ”é¬Æßéóé▒éŲéŲüAāoāŖāAæwé¬ĢsŚvé┼éĀéķé▒éŲüAāGābā`āōāOé╔éµé┴é─ē┴ŹHé┼é½éķé▒éŲüAé╚éŪ鬌L¢]ÄŗéĘéķŚØŚRéŠüB

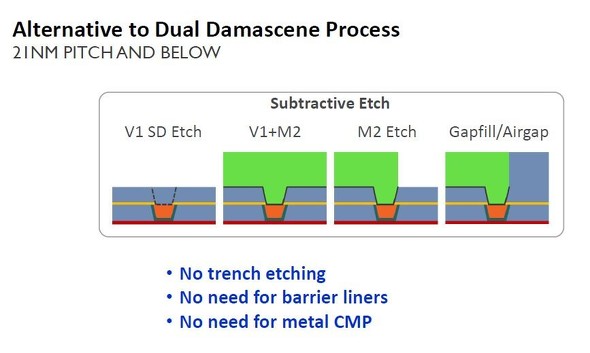

ü@é╗é▒é┼üuāZā~ā_ā}āVāōüiSemi-DamasceneüjüvéŲī─éįŗZÅpé╔éµé┴é─āŗāeājāEāĆüiRuüjé╠æĮæwözɳŹ\æóéŖJöŁÆåé┼éĀéķüBāZā~ā_ā}āVāōŗZÅpé┼é═üAē║æwé╠özɳæwé╠ÅŃé╔ÉŌēÅæwéɼ¢īéĄüAārāAéāGābā`āōāOé┼ī`ɼéĘéķüBé╗éĻé®éńÅŃæwé╠özɳæwüiRuæwüjéŲārāAéé▄éŲé▀é─ɼ¢īéĘéķüBé╗éĻé®éńārāAé╠ijł═éāGābā`āōāOéĄüAÉŌēÅ¢īé┼¢äé▀éķé®üAéĀéķéóé═āGāAāMāāābāvéŲéĄé─ÄcéĘüB

āZā~ā_ā}āVāōüiSemi-Damasceneüjé╠özɳī`ɼāvāŹāZāXüBɼ¢īéŲāGābā`āōāOé╔éµé┴é─özɳéŲārāAōdŗ╔éī`ɼéĘéķüBārāAé╠ijł═é═ÉŌēÅ¢īéĀéķéóé═āGāAāMāāābāvéŲé╚éķüBÅoōTüFimecüiIEDM2020é╠ā`āģü[āgāŖāAāŗŹuēēüuInnovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materialsüvé╠özĢzÄæŚ┐üj üiāNāŖābāNé┼ŖgæÕüj

üiĤē±é╔æ▒éŁüj

ü╦üuĢ¤ōcÅ║é╠āfāoāCāXÆ╩ÉMüvśAŹ┌āoābāNāiāōāoü[łĻŚŚ

Copyright © ITmedia, Inc. All Rights Reserved.

ŖųśAŗLÄ¢

āŗālāTāXüAŗ¤ŗŗŖmĢ█é┼21öN7ü`9īÄŖ·öäÅŃŹé2400ēŁē~¢┌ÄwéĘ

āŗālāTāXüAŗ¤ŗŗŖmĢ█é┼21öN7ü`9īÄŖ·öäÅŃŹé2400ēŁē~¢┌ÄwéĘ

āŗālāTāX āGāīāNāgāŹājāNāXé═2021öN7īÄ29ō·üA2021öN12īÄŖ·æµ2Älö╝Ŗ·üi4ü`6īÄüjŗŲÉčüiNon-GAAPāxü[āXüjéöŁĢ\éĄéĮüBæµ2Älö╝Ŗ·3āJīÄŖįé╠öäÅŃŹéé═2179ēŁē~é┼æOöNō»Ŗ·öõ30.7üōæØüAēcŗŲŚśēvé═614ēŁē~é┼ō»2.03ö{éŲæÕĢØé╚æØĹæØēvé╔é╚é┴éĮüBöäÅŃæŹŚśēvŚ”é═52.0üōüAēcŗŲŚśēvŚ”é═28.2üōéŠé┴éĮüB Źéæwē╗é╠īpæ▒é┼üAÉ╗æóāRāXāgéöÜē║é░éĘéķ3D NANDātāēābāVāģ

Źéæwē╗é╠īpæ▒é┼üAÉ╗æóāRāXāgéöÜē║é░éĘéķ3D NANDātāēābāVāģ

ŹĪē±é®éńé═üAö╝ō▒æ╠āüāéāŖé╠āAāiāŖāXāgé┼éĀéķMark WebbÄüé╠üuFlash Memory Technologies and Costs Through 2025üiātāēābāVāģāüāéāŖé╠ŗZÅpéŲāRāXāgé2025öNé▄é┼ōW¢]éĘéķüjüvéŲæĶéĘéķŹuēēé╠ŖTŚvéé▓ÅąēŅéĘéķüB ¢äé▀Ź×é▌DRAMé¬æÕŚeŚ╩āLāāābāVāģé╠É╗æóāRāXāgÆßīĖé╔ŹvīŻ

¢äé▀Ź×é▌DRAMé¬æÕŚeŚ╩āLāāābāVāģé╠É╗æóāRāXāgÆßīĖé╔ŹvīŻ

ŹĪē±é═DRAMéāŹāWābāNLSIé╔¢äé▀Ź×é▐ŗZÅpüueDRAMüvé╠É╗Ģiē╗Ä¢ŚßéēÉÓéĘéķüB æOÉiéĄæ▒é»éķIntel

æOÉiéĄæ▒é»éķIntel

Intelé═2021öN1īÄ21ō·üiĢ─ŹæÄ×ŖįüjüAŗŲÉčöŁĢ\éŹsé┴éĮüBé╗éĻéī®éķéŲüAō»Äąé╠ügÅI¢¢Ä×īvühé╠āJāEāōāgā_āEāōé╔üAÅŁé╚éŁéŲéÓÉöĢbé═ÆŪē┴é│éĻéĮéŲéóé”éķéŠéļéżüBéĮéŠéĄüAŖ«æSé╔ŖyŖŽÄŗé┼é½éķéĒé»é┼é═é╚é│é╗éżéŠüBāXāsāōāhāNā^ü[üiÅŅĢ±æĆŹņé¬ōŠłėé╚ÉlüjéĮé┐é═üAIntelé╠2020öNé╠ŗŲÉčé╠ā}āCāiāX¢╩éŠé»éŖ╚ÆPé╔ŗŁÆ▓éĘéķé▒éŲé¬é┼é½éķüBé▄éĮüAāvāēāX¢╩éµéĶéÓīćō_é╠Ģ¹é╔öĮē×éÄ”éĘōŖÄæēŲéĮé┐éÓéóéķüB HDDæÕÄĶWestern Digitalé╠ŗŲÉčüAæOöNō»Ŗ·öõé╠ēcŗŲŚśēvé¬3Älö╝Ŗ·śAæ▒é┼æØē┴

HDDæÕÄĶWestern Digitalé╠ŗŲÉčüAæOöNō»Ŗ·öõé╠ēcŗŲŚśēvé¬3Älö╝Ŗ·śAæ▒é┼æØē┴

ŹĪē±é═üAĢ─Western Digitalé╠2021ē’īvöNōxæµ1Älö╝Ŗ·é╠ŗŲÉčéÅąēŅéĘéķüB ÉVŹ▐Ś┐é┼ĤüXÉóæŃéæ_éżüuŗŁŚUōdæ╠āüāéāŖüiFeRAMüjüv

ÉVŹ▐Ś┐é┼ĤüXÉóæŃéæ_éżüuŗŁŚUōdæ╠āüāéāŖüiFeRAMüjüv

ŹĪē±é═üuŗŁŚUōdæ╠āüāéāŖüiFeRAMüjüvéĵéĶÅŃé░éķüBFeRAMé╠ŗLē»ī┤ŚØéŲüA60öNł╚ÅŃé╔ŗyéįŖJöŁé╠ŚÄjéÅąēŅéĄéµéżüB