2025年に「PCIe 7.0」策定へ、最大512GB/秒を目指す:車載分野も視野に

高速バスインタフェース「PCIe(Peripheral Component Interconnect Express)」仕様の第6版は2022年初めに発表されたばかりだが、同仕様を管理するPCI Special Interest Group(SIG)は既に「PCIe 7.0」を見据えている。

高速バスインタフェース「PCIe(Peripheral Component Interconnect Express)」仕様の第6版は2022年初めに発表されたばかりだが、同仕様を管理するPCI Special Interest Group(SIG)は既に「PCIe 7.0」を見据えている。

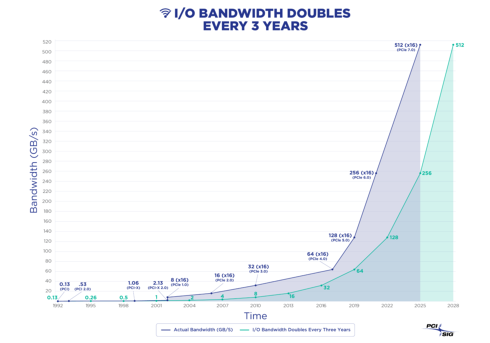

PCI-SIGは「PCI-SIG Developers Conference 2022」(2022年6月21〜22日、米国カリフォルニア州サンタクララ)で、2025年にPCIe 7.0をリリースすると発表した。PCI-SIGのプレジデント兼チェアマンを務めるAl Yanes氏は、「PCI-SIGのテクニカルワークグループは現在、データレートを128GT/秒に倍増し、x16構成では双方向で最大512Gバイト/秒にすることを目指して開発を進めている」と述べている。

PCI-SIGの第7版PCIeは、低レイテンシ(低遅延)と高信頼性の目標の実現と、電力効率の向上、前世代の全てのバージョンとの後方互換性の保持を続けることを目指している。次世代の仕様は、PAM4(Pulse Amplitude Modulation with 4 levels、4値パルス振幅変調)シグナルを採用し、チャネルパラメーターとリーチに焦点を当てるという。

Yanes氏は、「PCI-SIGは、PCIe 6.0成功の実績があるため、これらの目標を達成できると確信している」と述べている。PCIe 6.0は、NRZ(Non Return to Zero)シグナルからPAM4シグナルおよびフロー制御ユニットベースのエンコーディングに移行した。これによって、PAM4変調をサポートし、新たに追加されたFEC(前方誤り訂正)およびCRC(巡回冗長検査)と組み合わせることで、帯域の倍増を実現した。

同氏は、「NRZからPAM4への移行は、われわれにとって革命的な移行だった。これらの機能は、レイテンシや後方互換性を犠牲にすることなく追加された」と述べている。

PCIe 7.0の目標は、800GイーサネットやAI(人工知能)、機械学習、クラウドコンピューティング、さらには量子コンピューティングなど、PCI-SIGがターゲットとする新しいアプリケーションの要件に加え、ハイパースケールデータセンターや高性能コンピューティング、軍事および航空宇宙アプリケーションなどのデータ集約型のユースケースを反映している。

Yanes氏は、「言うまでもなく、全ての人がPCIe 7.0またはPCIe 6.0の帯域幅を必要としているわけではない。一方でHPC(High Performance Computing)やAI、機械学習の開発者は、より速い速度を採用して帯域幅の目標を達成しようとしている」と述べている。

PCI-SIGはこれ以外に、車載向けの機会も模索していく構えだ。車載市場への参入は、PCIe 6.0で既に視野に入れていたという。これについてYanes氏は、「ただし、PCIe 7.0の車載実装への道のりは、必ずしも明確にはなっていない。当社は、車載市場への参入に重点的に取り組んでいる」と述べる。

PCI-SIGでは、自動車に搭載されるセンサーの数を考慮し、自動車向けのワーキンググループを設置した。

現時点では、ISO 26262で認証されたASIL Dなどをサポートしていないため、PCIe 6.0すら車載アプリケーションには採用されていない。ASIL Dは車載向け安全規格の中でも最も厳しい規格の一つであり、取得には1年ほどかかるとYanes氏は説明した。

【翻訳:滝本麻貴、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

「PCIe 6.0」、最大データ伝送速度は64GT/秒

「PCIe 6.0」、最大データ伝送速度は64GT/秒

PCI技術の標準化団体であるPCI-SIG(PCI Special Interest Group)が、次世代バスインタフェース「PCI Express 6.0(PCIe 6.0)」を発表した。2021年に策定する予定だという。最大64GT/sの転送速度を実現する他、変調方式はPAM-4(4値パルス振幅変調)を採用する。既に使われている56G PAM-4が用いられている。 「組み込みメモリとメモリカードの中間」、キオクシアの新ストレージ製品

「組み込みメモリとメモリカードの中間」、キオクシアの新ストレージ製品

キオクシアはドイツ・ニュルンベルクで開催された組み込み技術の展示会「embedded world 2022」(2022年6月21〜23日)に出展し、「業界初」(同社)とする「XFM DEVICE(XFMD) Ver.1.0」規格準拠のリムーバブルストレージデバイス「XFMEXPRESS XT2」のデモを展示した。 車載対応の第4世代PCIeスイッチ、Microchip

車載対応の第4世代PCIeスイッチ、Microchip

Microchip Technology(以下、Microchip)は、ADAS(先進運転支援システム)アプリケーションに使用されるCPUとアクセラレーターのビルディングブロックを接続するために必要な低遅延と高帯域幅を提供する、車載対応PCI Express(PCIe)スイッチを発表した。 Micronの車載用LPDDR5がASIL Dの認証を取得

Micronの車載用LPDDR5がASIL Dの認証を取得

レベル5の自動運転実現への道のりは、当初の予測よりも長くなりそうだ。しかしMicron Technology(以下、Micron)は、あらゆるメモリコンテンツが未来の信頼性要件に対応できるよう、今から万全な準備を整えていく考えだという。 東陽テクニカ、800GbEに対応したテスターを発売

東陽テクニカ、800GbEに対応したテスターを発売

東陽テクニカは、800GbEに対応したSpirent Communications製のネットワークパフォーマンステスター「Spirent B1&B2 800Gアプライアンス」を発売した。 米新興企業、光I/OチップレットでNVIDIAと協業へ

米新興企業、光I/OチップレットでNVIDIAと協業へ

米国カリフォルニア州に拠点を置く新興企業Ayar Labsは、同社のチップ間光通信技術を中心としたエコシステムを構築するという。NVIDIAとの協業により、光I/O技術を適用した次世代アーキテクチャの開発に取り組んでいるところだ。