日本への投資を強化するTSMC、大阪にも研究開発拠点:2022年内にも開設(2/2 ページ)

TSMCは2022年9月2日、ハイブリッドで開催された「TSMC Technology Symposium Japan 2022」に併せて記者説明会を開催し、同社 ビジネスディベロップメント担当シニアバイスプレジデントのKevin Zhang氏が、TSMCの最先端の技術などを紹介した。

FinFETの種類を選べる「FINFLEX」アーキテクチャ

N3は、2022年後半の量産開始に向け開発が進んでいる。派生プロセスである「N3E」は、性能の向上と、低消費電力および、製造プロセスの複雑さを低減したもので、モバイルとHPCの用途に向ける。具体的には、「N5」プロセスの最初のバージョンに比べ、同等電力において18%高速化し、同等スピードにおいて消費電力は34%低減できる。ロジック密度は最大1.6倍で、チップ密度は最大1.3倍を実現するとしている。N3Eの量産開始は2023年後半を見込んでいる。

N3では、FinFETの種類を選べる「FINFLEX」アーキテクチャが導入される。性能重視の「3-2 FIN」、性能と電力効率のバランスを重視した「2-2 FIN」、超低消費電力の「2-1 FIN」の3種類のFinFETを用意していて、顧客は用途に合わせ、これらのFinFETベースの回路ブロックを組み合わせることができる。

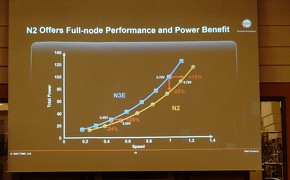

その先に控えている「N2」プロセスでは、ナノシートを用いたGAA(Gate-All-Around)トランジスタ構造を導入する。N3Eに比べ、10〜15%の高速化と、25〜30%の省電力化、1.1倍以上のチップ密度を実現できるとする。先述した通り、2025年の量産開始を目指す。

シート状の半導体材料にも期待

ナノシート以降は、CFET(Complementary FET/相補型FET)の導入や、2次元構造のTMD(遷移金属ダイカルコゲナイド)、CNT(カーボンナノチューブ)の活用も含めて、さまざまなトランジスタ構造の可能性を探るとZhang氏は述べた。CFETは、n型FETとp型FETを上下に積層してCMOSを構成する構造。左右ではなく上下に重ねることで、従来よりも大幅な面積縮小と高速化を図れる技術として注目されている。TMDは、モリブデン(Mo)やタングステン(W)などの遷移金属原子と、硫黄(S)やセレン(Se)といったカルコゲン原子から構成されるシート状の材料で、次世代の半導体材料として以前から期待されている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

TSMCが2nmにナノシート採用、量産開始は2025年を予定

TSMCが2nmにナノシート採用、量産開始は2025年を予定

TSMCは、2025年に量産を開始する次の2nmノードの生産にナノシート技術を採用した。それにより、HPC(High Performance Computing)システムにおけるエネルギー消費の削減を狙う。 TSMC、「N4」プロセスの量産を2022年に開始

TSMC、「N4」プロセスの量産を2022年に開始

TSMCは2020年8月24〜26日に年次イベント「TSMC 2020 Technology Symposium」をオンラインで開催し、現在「N5」プロセス適用製品の生産を拡大していく中で、「N4」プロセスを開発したと発表した。2021年に生産を開始し、2022年には量産に着手する予定だという。 首都大学東京ら、TMDの新たな合成技術を開発

首都大学東京ら、TMDの新たな合成技術を開発

首都大学東京と筑波大学の研究チームは、新たに開発した遷移金属ダイカルコゲナイド(TMD)の合成技術を用いて、半導体原子層の接合構造(半導体ヘテロ接合)を実現し、その構造と電気的性質を解明した。 「中国に対抗する」CHIPS法成立で、激化する米中半導体戦争

「中国に対抗する」CHIPS法成立で、激化する米中半導体戦争

米国のジョー・バイデン大統領が半導体の国内製造を促進する法律「CHIPS and Science Act」(CHIPS法)が成立しました。同法は、米中の半導体製造にどのような影響を与える可能性があるのでしょうか。 IntelのtGPU生産遅延、TSMCの3nmプロセス展開にも影響

IntelのtGPU生産遅延、TSMCの3nmプロセス展開にも影響

アナリストによると、Intelが近々発表を予定していたプロセッサ「Meteor Lake(開発コード)」に搭載するGPUチップレットの生産に遅れが生じているという。これによって、TSMCの3nmプロセス技術のロールアウトにも遅延が発生する見込みだ。 2PFLOPS超えのGPGPUを開発した、中国新興企業

2PFLOPS超えのGPGPUを開発した、中国新興企業

2022年8月21〜23日にオンラインで開催された「Hot Chips」において、中国の新興企業Biren Technology(以下、Biren)がステルスモード(製品や開発の中身を明らかにしないこと)を脱し、データセンターにおけるAI(人工知能)学習と推論向けの大型汎用GPU(GPGPU)チップの詳細を明らかにした。同社の「BR100」は、TSMCの7nmプロセス技術に基づく537mm2のチップレット2つで構成されている他、CoWoS(Chip on Wafer on Substrate)パッケージに4つのHBM2eを積層している。