パッケージのサイズからは判別不能 「シリコン面積比率」が示す高密度実装:この10年で起こったこと、次の10年で起こること(79)(3/3 ページ)

近年、半導体ではパッケージの高密度化が進んでいる。パッケージのサイズからは、搭載されているシリコンの“総面積”は分からない。今回は、2023年に登場した話題のプロセッサを、「パッケージ面積に対するシリコン面積の比率」という観点で見てみよう。

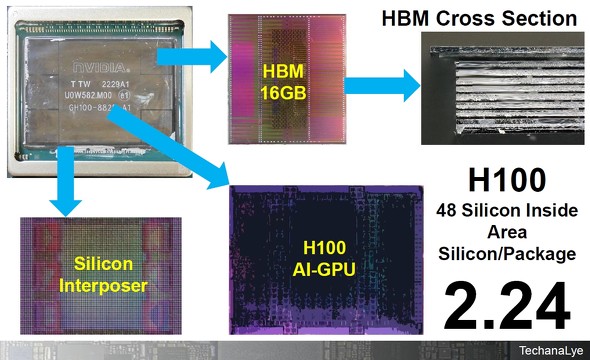

モバイルチップ並みの高いシリコン比率を持つNVIDIA「H100」

図3はNVIDIAの「H100」(80GB版)の様子である。詳細はぜひ、有償のテカナリエレポートで見ていただきたい。内部には48個ものシリコンが入っている。上記と同じ基準で算出したシリコン比率は、2.24となっている。モバイルチップであるA17 Pro並みの高いシリコン比率を実現していることが分かる。メモリの積層とシリコンインターポーザーが高いシリコン比率に結びついているわけだが、今後メモリ容量(積層)が増えていくとモバイル超えのシリコン比率になっていくことは間違いないものと思われる。

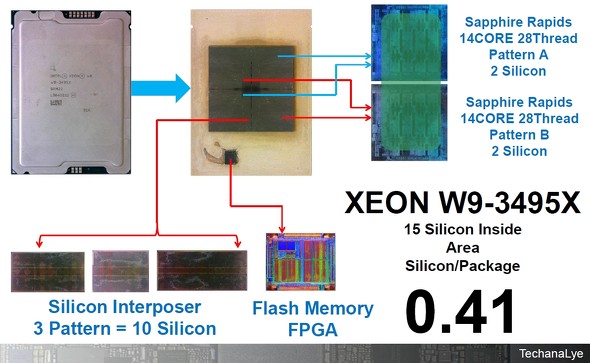

IntelとAMDのチップのシリコン比率は?

図4は、2023年に発売されたIntelの最上位チップ「Xeon w9-3495X」の様子である。4つのプロセッサを組み合わせ、各プロセッサを接続する部分シリコンインターポーザー、FPGAを搭載した構成となっている。シリコンは15個、シリコン比率は0.41となっている。一部シリコンインターポーザーで積層されている場所もあるが大半は平置き。シリコン比率はメモリを内蔵するA17、M3、H100に比べて1桁小さいものとなっている。シリコン効率は低い。

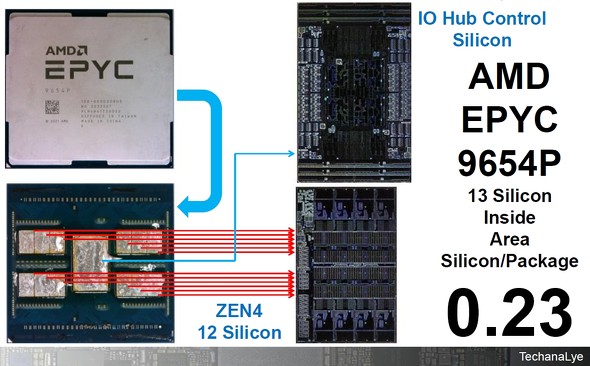

図5は、2022年末に発売されたAMDの「EPYC 9654P」である。13シリコン(CPUが12個、I/Oチップが1個)で構成されておりシリコン比率は0.23となっている。全シリコンが平置きのチップレットになっている。

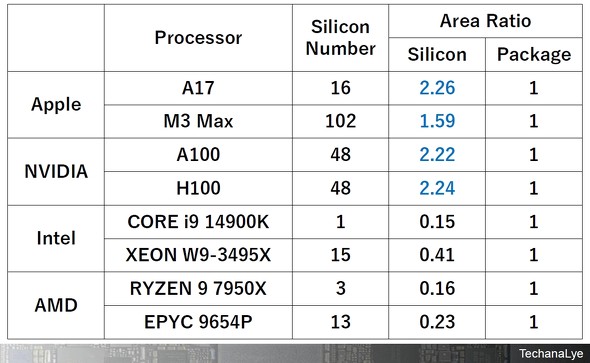

表3は、今回報告した3チップの情報を含めた、代表的なプロセッサのシリコン数およびシリコン比率である。今後、チップレット化が進むと思われるが、シリコン使用の高効率化、高集積化を進める上で、メモリの取り込みや積層箇所の多用がより重要になっていくことは間違いないだろう。従来型はシリコン比率1を割っており(チップレットも平置きだけでは1を超えない)、高密度実装とは言えないものとなっている。現在も、多くの取り組みや研究が進められている(弊社も一部関与)。ぜひロジック系でも将来的にはシリコン比率3、4超えを目指していただきたい。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

「S9」のベースは「A16 Bionic」!? Appleの自在過ぎるスケーラブル戦略

「S9」のベースは「A16 Bionic」!? Appleの自在過ぎるスケーラブル戦略

Appleのプロセッサ開発力は、スピードを含め確実に上がっている。さらにAppleは、コア数を自由自在に増減し、ローエンドからスーパーハイエンドまでのプロセッサファミリーをそろえる「スケーラブル戦略」を加速している。発売されたばかりの「Apple Watch Series 9」を分解すると、それがよく分かる。 それでもスマホの技術進化は続いている、「iPhone 15 Pro Max」「Mate 60 Pro」を分解

それでもスマホの技術進化は続いている、「iPhone 15 Pro Max」「Mate 60 Pro」を分解

今回は、2023年夏に発売された話題のスマートフォン、Apple「iPhone 15 Pro Max」とHuawei「Mate 60 Pro」の分解結果を報告する。 Apple M2 Ultraと「たまごっち ユニ」から見える、米中半導体の位置付け

Apple M2 Ultraと「たまごっち ユニ」から見える、米中半導体の位置付け

今回は、Appleのモンスター級プロセッサ「M2 Ultra」と、バンダイの「Tamagotchi Uni(たまごっち ユニ)」を分解。そこから、米中の半導体メーカーが目指す戦略を読み解く。 スマホやPCは「中身のみ進化」する時代に突入

スマホやPCは「中身のみ進化」する時代に突入

今回は、Appleの「Mac Pro」と「Mac Studio」や、ソニー、Samsung Electronicsのスマートフォンを分解。いずれも「外観は前世代品と同じ」で、中身を大きく変更していることが共通している。 1つのCPUを作って「完コピ」、Appleの理想的なスケーラブル戦略

1つのCPUを作って「完コピ」、Appleの理想的なスケーラブル戦略

Appleのプロセッサ「M2」シリーズが出そろった。今回は、そのM2シリーズの解析結果から、Appleのチップ開発戦略をひもといてみよう。 最新チップを徹底比較! 〜最新スマホから復刻版ゲーム機まで

最新チップを徹底比較! 〜最新スマホから復刻版ゲーム機まで

2022年第4四半期から2023年第1四半期に発売された最新プロセッサのうち、スマートフォン向けチップや、復刻版ゲーム機などに搭載されているチップを比較してみたい。