3端子貫通型フィルタの接続方法と実装レイアウト:福田昭のデバイス通信(454) 2022年度版実装技術ロードマップ(78)(2/2 ページ)

今回は「(2)3端子貫通型フィルタの接続と実装のポイント」の概要を説明する。3端子貫通型フィルタを電源ラインに接続する2つの方法と、それぞれの用途を解説する。

電源ラインの高周波雑音を取り除くフィールドスルー接続

多層プリント基板の電源ラインと直列に3端子貫通フィルタを接続する「フィールドスルー接続」では、高周波雑音を除去する効果が期待できる。ただし、多層プリント基板のレイアウトによってはプリント基板のESL成分によってフィルタの効果が弱まることがある。推奨されるのは以下のようなレイアウトである。

多層プリント基板の第1内層(表面層のすぐ下の層)はグランドプレーン(接地平面)層、その下は電源ライン層とする。3端子貫通フィルタは表面層に搭載する。フィルタの入出力端子はスルーホールを介して電源ライン層に、接地端子はビアを介して接地プレーン層に接続する。電源プレーン層の一部は、入力と出力が短絡しないように切除しておく。接地端子とグランドプレーン層の接続では、ビアをなるべく太く短くする。

シャントスルー接続で電源電圧の変動を抑える

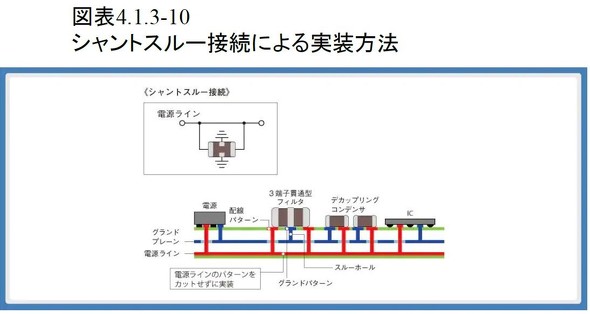

多層プリント基板の電源ラインと並列に3端子貫通フィルタを接続する「シャントスルー接続」では、電源電圧の突発的な変動を抑える効果が期待される。すなわち負荷電流の急激な上昇によって電源ラインの電圧が低下したときに、3端子貫通フィルタから電源ラインに電流を一時的に供給する。

多層プリント基板のレイアウトと3端子貫通フィルタの搭載レイアウトは、フィールドスルー接続とほとんど変わらない。大きな違いは、入出力端子をつなぐ電源プレーン層を除去しないことだ。電源プレーンをカットしないことで、並列接続となる。シャントスルー接続には、3端子貫通フィルタ内部の寄生抵抗の影響が少ないというメリットもある。

3端子貫通フィルタを電源電圧安定化に利用すると、同じ用途で使われるデカップリングコンデンサの数を減らすことができる。例えば1005Mサイズの積層セラミックコンデンサ(MLCC)4個と同等の機能を、1個の1608Mサイズ3端子貫通フィルタで置き換えられる。実装面積は2.99mm2から1.28mm2へと半分以下に減る。

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

チップ抵抗器の小型化が過度な温度上昇を招く(前編)

チップ抵抗器の小型化が過度な温度上昇を招く(前編)

今回から、第4章第1節第3項「部品実装・設計時の注意点」の概要を説明していく。この項は、「熱設計」「電気性能」などの4つのパートで構成される。 表面実装型電子部品(SMD部品)の開発動向(後編)

表面実装型電子部品(SMD部品)の開発動向(後編)

後編となる今回は、「セラミックコンデンサの高容量化・低ESR化、薄型化」や「チップ抵抗器の高電力化」について解説する。 プロセッサやメモリなどの進化を支えるパッケージ基板

プロセッサやメモリなどの進化を支えるパッケージ基板

今回は第3章第4節第8項(3.4.8)「パッケージ基板」の概要を説明する。パッケージ基板の変遷と、パッケージ基板に対する要求仕様のロードマップを解説する。 表面実装型電子部品(SMD部品)の小型化トレンド

表面実装型電子部品(SMD部品)の小型化トレンド

JEITA「2022年度版 実装技術ロードマップ」を解説するシリーズ。今回から、第4章「電子部品」の概要を説明していく。 プリント基板の「弁当箱」からパッケージとチップまで、電磁シールド技術が進化

プリント基板の「弁当箱」からパッケージとチップまで、電磁シールド技術が進化

JEITA「2022年度版 実装技術ロードマップ」の「パッケージ組立プロセス技術動向」について解説するシリーズ。今回は第3章第4節第6項(3.4.6)「電磁シールド」の概要を説明する。 シリコンダイを光や熱、ホコリ、機械衝撃などから保護する樹脂封止技術

シリコンダイを光や熱、ホコリ、機械衝撃などから保護する樹脂封止技術

今回は第3章第4節第5項(3.4.5)「樹脂封止技術(アンダーフィル、モールディング)」の概要を説明する。