連載

コンデンサの振動対策とクラック対策:福田昭のデバイス通信(455) 2022年度版実装技術ロードマップ(79)(2/2 ページ)

今回は「4.1.3.3 信頼性」の概要を説明する。その中から、「振動対策」と「クラック対策」を取り上げる。

積層セラミックコンデンサのクラック対策

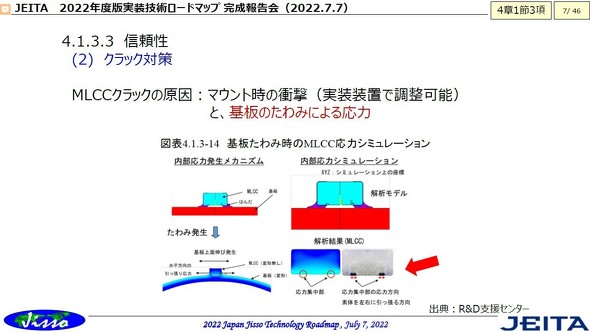

「(2)クラック対策」では、積層セラミックコンデンサ(MLCC)のクラック(ひび割れ)を取り上げた。主な原因は、実装基板が曲がる(たわむ)ことによる機械的な応力である。実装基板が曲がる原因には、はんだ付け、電気的検査、基板分割などがある。基板がたわむと外部電極によってMLCCに引っ張り応力が加わる。応力は外部電極付近に集中しており、この領域からクラックが発生する。

クラックが発生すると、静電容量の低下、絶縁抵抗の著しい上昇(オープン状態)、絶縁抵抗の低下、短絡(ショート状態)といった不具合が起こる。

積層セラミックコンデンサ(MLCC)のクラック発生メカニズムと応力の解析結果[クリックで拡大] 出所:JEITA Jisso技術ロードマップ専門委員会(2022年7月7日に開催された完成報告会のスライド)

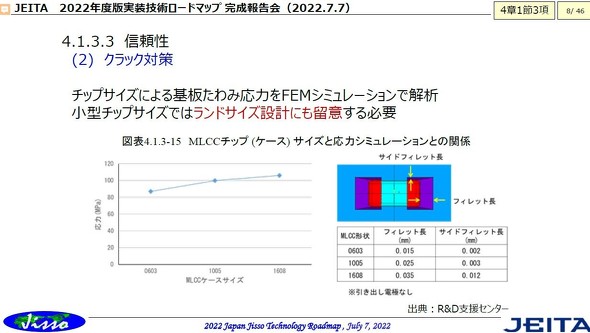

MLCCのチップサイズと基板のたわみによる応力の関係をシミュレーションすると、サイズが小さくなるにつれて応力も小さくなる傾向がある。ただし応力はランドサイズにも依存するので、ランド設計には注意が必要だ。

MLCCのチップサイズと応力(左)、はんだフィレットサイズ(右下)の関係[クリックで拡大] 出所:JEITA Jisso技術ロードマップ専門委員会(2022年7月7日に開催された完成報告会のスライド)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

3端子貫通型フィルタの接続方法と実装レイアウト

3端子貫通型フィルタの接続方法と実装レイアウト

今回は「(2)3端子貫通型フィルタの接続と実装のポイント」の概要を説明する。3端子貫通型フィルタを電源ラインに接続する2つの方法と、それぞれの用途を解説する。 チップ抵抗器の小型化が過度な温度上昇を招く(前編)

チップ抵抗器の小型化が過度な温度上昇を招く(前編)

今回から、第4章第1節第3項「部品実装・設計時の注意点」の概要を説明していく。この項は、「熱設計」「電気性能」などの4つのパートで構成される。 表面実装型電子部品(SMD部品)の開発動向(後編)

表面実装型電子部品(SMD部品)の開発動向(後編)

後編となる今回は、「セラミックコンデンサの高容量化・低ESR化、薄型化」や「チップ抵抗器の高電力化」について解説する。 プロセッサやメモリなどの進化を支えるパッケージ基板

プロセッサやメモリなどの進化を支えるパッケージ基板

今回は第3章第4節第8項(3.4.8)「パッケージ基板」の概要を説明する。パッケージ基板の変遷と、パッケージ基板に対する要求仕様のロードマップを解説する。 表面実装型電子部品(SMD部品)の小型化トレンド

表面実装型電子部品(SMD部品)の小型化トレンド

JEITA「2022年度版 実装技術ロードマップ」を解説するシリーズ。今回から、第4章「電子部品」の概要を説明していく。 プリント基板の「弁当箱」からパッケージとチップまで、電磁シールド技術が進化

プリント基板の「弁当箱」からパッケージとチップまで、電磁シールド技術が進化

JEITA「2022年度版 実装技術ロードマップ」の「パッケージ組立プロセス技術動向」について解説するシリーズ。今回は第3章第4節第6項(3.4.6)「電磁シールド」の概要を説明する。