連載

半導体チップの高密度3次元積層を加速するハイブリッド接合:福田昭のデバイス通信(442) 2022年度版実装技術ロードマップ(66)(2/2 ページ)

今回から、第3章第4節(3.4)「パッケージ組立プロセス技術動向」の内容を紹介する。本稿では、ハイブリッドボンディングを解説する。

位置合わせの精度が極めて重要

ハイブリッドボンディングでは、2枚のウエハーの位置合わせ(重ね合わせ)精度が極めて重要である。電極の位置合わせ誤差は100nm以下が要求される。

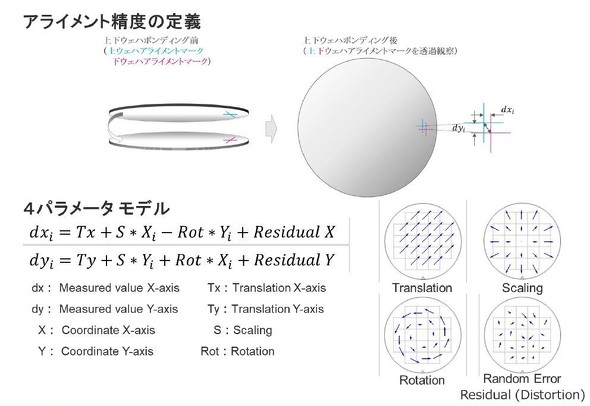

位置合わせ誤差(重ね合わせ誤差)は以下の4つの成分の合計で決まる。位置の相対的なずれ、回転、伸縮、その他、である。はじめの3つは、ウエハーのボンディング装置で補正をかける。最後の1つは、ウエハープロセスとボンディング装置の両方から最小化する。

ウエハー積層の位置合わせ(アラインメント)誤差の定義。横方向(x方向)と縦方向(y方向)の誤差で定義する。相対的なずれ(translation)、回転(rotation)、伸縮(scaling)、その他(residual)の4つの誤差要因をモデル化し、合計する[クリックで拡大] 出所:JEITA Jisso技術ロードマップ専門委員会(2022年7月7日に開催された完成報告会のスライド)

2022年の時点で量産に使われるハイブリッド接合の位置合わせ誤差は150nmとされる。10年後の2032年には、誤差は半分以下の70nmに減るとロードマップでは予測する。

ウエハー積層の位置合わせ(アラインメント)誤差ロードマップ(2022年〜2032年)[クリックで拡大] 出所:JEITA Jisso技術ロードマップ専門委員会(2022年7月7日に開催された完成報告会のスライド)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

エリアアレイ表面実装パッケージ(BGA)のロードマップ

エリアアレイ表面実装パッケージ(BGA)のロードマップ

今回は、第3章第3節第10項(3.3.10)「その他の表面実装パッケージ」の概要を説明する。 4Gから5Gミリ波の移動体通信向けフロントエンドパッケージ(後編)

4Gから5Gミリ波の移動体通信向けフロントエンドパッケージ(後編)

後編となる今回は、誘電体材料パターニング方法とAiP(Antenna in Package)の概要を紹介する。 車載パワーデバイスの出力密度向上手法

車載パワーデバイスの出力密度向上手法

今回は、第3章第3節第4項「車載パワーデバイス」から、「パワーデバイスの発展」を解説する。 プリント基板に半導体チップを埋め込む部品内蔵基板

プリント基板に半導体チップを埋め込む部品内蔵基板

今回は、FO-WLP(Fan Out-Wafer Level Package)のロードマップと、FO-PLP(Fan Out-Panel Level Package)の一種ともみなせる部品内蔵基板について解説する。 多ピン小型パッケージ「FO-WLP」の信頼性問題とその対策

多ピン小型パッケージ「FO-WLP」の信頼性問題とその対策

今回は初期の「FO-WLP」で生じた信頼性の問題と、問題を解決した組み立てプロセス、再配線層(RDL)を微細化したプロセスを解説する。 超多ピンと複数ダイ搭載を両立させた小型パッケージFO-WLP

超多ピンと複数ダイ搭載を両立させた小型パッケージFO-WLP

引き続き、各種パッケージ技術の動向を紹介する第3章第3節を取り上げる。今回から「3.3.2.2 FO-WLP、FO-PLP、部品内蔵基板」の概要を紹介する。