進化したスタック・ダイ技術 ―― ピン数やフットプリント、システムの複雑性の問題をどう解決したのか?:フラッシュメモリの容量問題を解決

近年、フラッシュメモリは単一パッケージ内にメモリダイをスタックし、小さなフットプリントでメモリ容量を増やしています。本記事では、複数のフラッシュメモリICを1つのスタック・ダイ・パッケージに置き換えた場合の影響を概説し、ウィンボンドが開発したスタック・ダイの新技術が、他のソリューションと比べていかに高性能で、なおかつピン数および、フットプリントの削減を実現したかという点について説明します。

消費者の要求や重要なポイントは常に変化し続けています。モバイル機器、コンピューター機器のユーザーは、より小型で軽量かつ、洗練された製品を常に探しており、さらに多くの機能と優れた性能を要求します。かつてラップトップPCで必要とされていたアプリケーションはスマートフォンに移行し、スマートフォンのみ対応していたアプリケーションも、今日ではスマートウォッチでサポートされています。

設計者たちは、絶え間ない小型化要求に応えるため、新たな方法を評価し続けます。その際のトッププライオリティの1つがシステムストレージです。コードストレージ用に使用されるシリアルNORフラッシュメモリと、データストレージ用および、コードのバックアップ用に使用されるシリアルNANDフラッシュメモリを用いることは、スペースが限られたデザインにおいて、比較的大きな基盤面積を占領することになります。

ウィンボンドは、シリアルNORおよび、シリアルNANDフラッシュIC生産量で世界有数のシェアを誇り、フラッシュメモリとホストおよび、システムオンチップ(SoC)、マイクロプロセッサ、マイクロコントローラ間における非常に高速な読み出し/書き込み動作が可能な標準シリアルペリフェラルインタフェースの高帯域幅バージョンであるQuad Serial Peripheral Interface(QSPI)を考案し、この問題の解決に貢献しました。ウィンボンドのQSPIは、はるかに少ないチャンネルとより小さなパッケージを用いながらもパラレルフラッシュのデータスルーレートに匹敵し、このイノベーションはシステムボード上のメモリ専有面積の小型化において重要なステップとなりました。

近年、シリアルフラッシュメーカーは、単一パッケージ内にフラッシュメモリダイをスタックすることでフットプリントを減らしつつメモリ容量を増やす方法も取り入れています。

この記事では、複数のフラッシュメモリICを1つのスタック・ダイ・パッケージに置き換えた場合の影響を概説し、ウィンボンドが開発したスタック・ダイの新技術が、他のソリューションと比べていかに高性能で、なおかつピン数および、フットプリントの削減を実現したかという点について説明します。

スタック・ダイの利点

小型デバイス設計における典型的なフラッシュメモリの使用例は、コードストレージ用の16MビットシリアルNORフラッシュデバイスと、データおよび、Linuxオペレーティングシステム用の1GビットシリアルNANDフラッシュデバイスで構成されています。NORフラッシュは優れたランダムアクセスパフォーマンスや耐久性、リテンション、さらに頻繁に読み取られるコードを格納するための重要な機能を提供します。NANDフラッシュはよりスピーディなプログラミングを提供し、容量512Mビット以上はNORフラッシュよりも安価です。読み出し時の遅延時間は長くなりますが、データアクセス頻度が低いことを考えると、これは許容範囲内と言えるでしょう。

通常のシステム設計においてボード上に2つのフラッシュメモリパッケージを実装する必要があり、それぞれに独自のSoCインタフェースを持ちます。

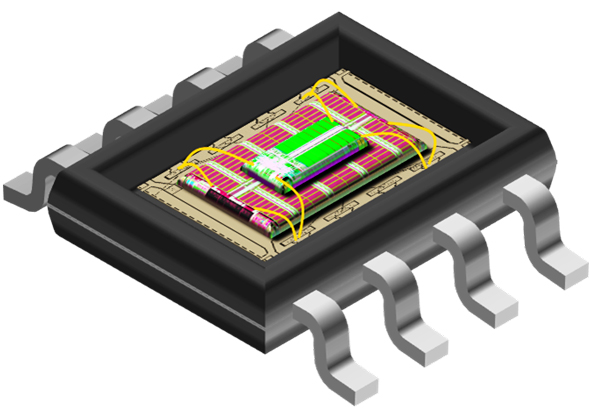

本使用例では、スタック・ダイ・パッケージを使用することで、簡単にフットプリントを減らすことが可能です(図1参照)。異種組み合わせのパッケージにおいて、小型のNORフラッシュは、それより大きいサイズのNANDフラッシュダイの上にスタックされます。

NORの上にNOR、あるいはNANDの上にNANDをスタックするような、同種組み合わせのパッケージでも同様のメリットが得られます。例えば、512MビットのNANDフラッシュを使用する既存の製品設計において追加データ容量を必要とした場合、512MビットのICを1Gビット品に置き換えるというのが従来のアプローチでしょう。しかし、1Gビットデバイスのフットプリントとピン配置が異なると、ボードの再設計に時間がかかります。

同種組み合わせのパッケージはこのボード設計の手間を省いてくれます。512Mビットが2枚スタックされているものは、512Mビットのシングルダイと同じピン配置にて同じパッケージに収容可能なため、ボード再設計をしなくても即座にメモリ容量を倍増できるのです。

この基板フットプリントの再作成が不要および、開発リソース削減の2つのメリットは、スタックダイコンセプトならではのものです。

ウィンボンドは、フラッシュメモリにおいて新たなスタック・ダイのアプローチを導入しました。これはボードのフットプリントをさらに大幅に削減すると同時に、リード/ライト性能を向上させます。

少ピンカウントのスタックド・パッケージ

スタック・ダイ製品を実装する際の主な課題の1つとして、SoCやマイクロコントローラと、フラッシュメモリパッケージ内の2つ(またはそれ以上)のダイの間にインタフェースを提供する点が挙げられます。SPIバス上の競合を避けるため、SoCはチップセレクト(CS)コマンドを使用してどのダイがインタフェースとして有効かをスタックド・パッケージに伝えます。

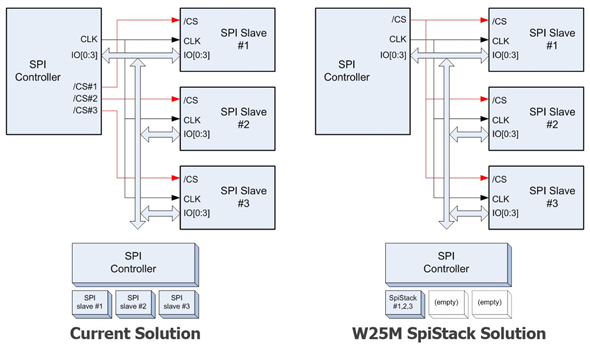

その他のスタックメモリソリューションでは、このCSファンクションは専用CSライン(各ダイ1本ずつ)を介してハードウェアに実装されます。つまり、2つのダイを含むパッケージには2本の、3つのダイには3本のCSラインがあります。

これは、メモリデバイスやSoCのピン数増加、またボード上により多くの配線を必要とする点を考えると不便な状態であることは明らかです。

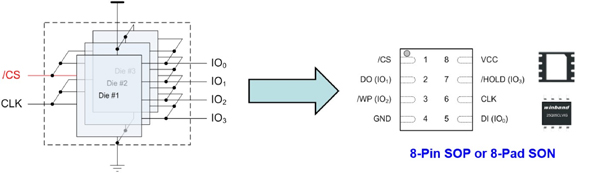

ウィンボンドの新たなW25M SpiStackフラッシュメモリ製品は、メモリデバイスとSoC間において単一CSチャネルで動作が可能なソフトウェアチップセレクト機能を用いることによりこの問題を解決しています(図2参照)。SpiStackパッケージに含まれるダイはそれぞれダイIDを持ち、シンプルなチップセレクトコマンドと関連するダイIDを用いて、SpiStackパッケージ内のどのチップがSPIバスを使用するかを全てのダイに伝えます。

このソフトウェアCS機能は、メモリデバイスやSoC上の単一CSピンのみを介して操作し、それらの間に1つのCS配線のみを必要とします。ピン数の削減により、標準8ピンSOP、または8パッドSONパッケージ内に2〜4ものダイ収容が可能になります。ハードウェアCS機能を使用するスタック・ダイ実装は、通常16ピンSOPや24ボールBGAであり、より大きくより複雑な基板設計が必要になります(図3参照)。

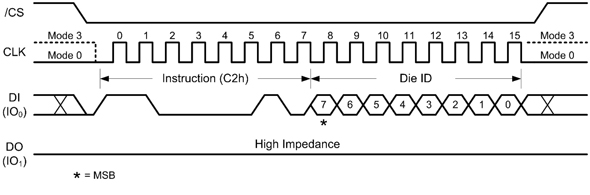

設計者がSpiStackのCS機能をシステムソフトウェアに統合することは簡単です。C2hコマンドはフラッシュメモリパッケージ内のあらゆるダイの選択に使用されます(図4参照)。アクティブダイを変更するために、ダイの動作状況に関係なく、いつでもC2hコマンドを発行することができます。選択された1つのダイのみがSPIバス上でアクティブになります。

スピーディな読み出し/書き込み動作

フラッシュメモリは本来、SRAMやDRAMと比べプログラミング動作に時間がかかります。シングルダイのフラッシュを使用する際、書き込みの最中にシステムがメモリの読み出しを行うことがよく起こります。すると、コントローラはまず書き込み中断コマンドを発行し、メモリ読み出しコマンド、書き込み再開コマンドを次々に発行する必要があります。フラッシュメモリを複雑に使用するため、読み出しと書き込みの処理が遅くなるのです。

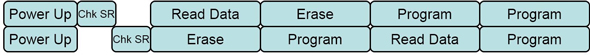

ウィンボンドは、SpiStack製品に同時実行機能を新たに導入し、このボトルネックを解消しています。SpiStack製品内の1つのダイが異なるダイからの読み出し動作を行っている最中にも、SoCは書き込みや消去動作を行うことが可能なのです(図5参照)。

上記の通り、SPIバスがいつでもアクセスできるダイは1つだけですが、SpiStackデバイスは、複数ダイがそれぞれ書き込み、読み出し、消去動作を同時に実行することが可能です。

多くのアプリケーションにおいて、このメモリ同時実行機能はオペレーション速度を大幅に向上させます。つまり、SpiStackデバイスは、シーケンシャルモードのみで実行される同等デバイスより迅速なオペレーションを可能にするのです。

同種、異種の豊富な品ぞろえ

SpiStackマルチダイパッケージは、NOR+NANDの異種構成や、NOR+NOR、NAND+NANDの同種構成があり、それぞれ幅広い種類のパッケージタイプおよび、容量を取りそろえています。ウィンボンドは、世界最大のシリアルフラッシュメーカーとして、幅広いメモリ容量とパッケージオプションをシステム設計者に提供します。

デザインに柔軟性を与え、メモリ容量の変更要件に合わせ、共通のフットプリントおよび、ピン配置にてデバイスを置き換えることが可能になります。

販売中のSpiStackデバイスの一例は以下の通りです。

- 16Mビット NOR + 1Gビット NAND

- 512Mビット NOR(256Mビット NOR×2)

- 2Gビット NAND(1Gビット NAND×2)

ウィンボンドのSpiStackロードマップ内では、2017年中に、またお客さまのご要求に応じて、さらに多くの組み合わせにて供給する予定です。

商品の詳細については、Winbond SpiStack Flashをご参照ください。

【著者】

・K.C. Shekar/ウィンボンド・エレクトロニクス アメリカ(シニアディレクター/戦略マーケティング部)

・神永 雄大/ウィンボンド・エレクトロニクス株式会社(アシスタントプロフェッショナルマネジャー)

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

提供:ウィンボンド・エレクトロニクス株式会社

アイティメディア営業企画/制作:EE Times Japan 編集部/掲載内容有効期限:2017年12月20日

関連記事

自動車での利用が広がっているフラッシュメモリは、機能安全規格「ISO26262」を満たす必要性が高まっています。機能安全規格を満たすために必要な機能、要件とはどのようなものかを紹介しながら、機能安全規格を満たす最新フラッシュメモリを紹介していきます。

フラッシュメモリは、セキュリティ上の脆弱性により、IPの盗難による商業的損害や、悪質なリバースエンジニアリングによる模造品の製造などの危機にさらされています。そこで、フラッシュメモリを正当なホストコントローラとユニークかつ、安全にペア接続させる方法について概説します。

モバイル機器やウェアラブル機器などあらゆる機器は、消費電力を低減するためにデバイス動作電圧の低電圧化が進みつつあります。そうした中で、1.2Vや1.5Vで動作する低電圧メモリが登場しています。今回は、ウィンボンド(Winbond)が展開する低電圧メモリを取り上げながら、低電圧メモリの利点や活用法を紹介しましょう。

図1:小型なNORフラッシュがそれより大きなNANDフラッシュの上にスタックされている。ダイおよび、ボンドワイヤは、リードフレーム、またはパッケージ基板に実装可能。(画像著作権:ウィンボンド)

図1:小型なNORフラッシュがそれより大きなNANDフラッシュの上にスタックされている。ダイおよび、ボンドワイヤは、リードフレーム、またはパッケージ基板に実装可能。(画像著作権:ウィンボンド)

図5:SpiStackデバイスでは1つのダイがSPIバスを占有し、別のダイは書き込みまたは消去動作を実行。(画像著作権:ウィンボンド)

図5:SpiStackデバイスでは1つのダイがSPIバスを占有し、別のダイは書き込みまたは消去動作を実行。(画像著作権:ウィンボンド)