Armコアは低コストで導入できる! 「DesignStart」の活用で:初期費用も2段階に設定

SoCの開発コストが増加する中、Armが2010年から始めているのが「DesignStart」という取り組みだ。同社のコア「Cortex-M0」をライセンス無償で提供するというもので、設計時間の短縮やIP(Intellectual Property)コストの低減を図ることができる。Armは、Armコアを採用する裾野を広げるべく、DesignStartの拡充に注力している。

ご存じの通り、Armはプロセッサや周辺回路のIP(Intellectual Property)を顧客に提供し、顧客はそのIPを組み込んで自身のSoC(System on Chip)を開発するというビジネスモデルを採っている。だが、昨今ではSoCの開発費用が次第に高騰しつつあるため、ASSPを作る半導体メーカーはともかく、自社製品向けのSoCを作る一般企業をはじめ、スタートアップや中小企業などではSoCを作るのは、特にコストの面で難しくなりつつある。

こうした状況は昨日今日に始まった話ではなく、ここ10年くらいずっといわれていた。SoC開発のための初期費用が数百万とか1千万円で済んでいたのはもう20年くらい前の話であり、10年ほど前からは最低でも1億円程度の金額が必要になっている。

この1億円の中には、ファウンドリーで利用するマスク製造のコストなども含んでいるが、それ以外に設計に掛かる人件費やEDAツールの費用、そしてIPの費用も含んでいる。この初期費用は当然最終製品のコストに載る形になるが、少品種大量生産から多品種少量生産に市場のトレンドが変化してゆくと、結果的に最終製品のコストが高騰することになる。

初期コストを抑えてSoC開発のリスクを下げる、「DesignStart」

こうした状況に一石を投じるべく、Armが2010年から始めているのが「DesignStart」と呼ばれる取り組みだ。当初は限定バージョン(省電力への最適化や機能構成が一部制限された)の「Cortex-M0」を試作用に提供するものだったが、2017年からDesignStartポータル経由でCortex-M0をライセンス無償で提供する商用版も追加になった。このCortex-M0を組み込んだSoC製造を行うことで、設計時間の短縮やIPコストの低減を図ることができるようになった。もちろん、これを利用すれば初期コストが半分になるか、といえばそこまでは下がらないだろうが、特にスタートアップ企業などの場合はASICの製造そのものが結構なリスクになるので、初期コストを抑えることでこのリスクを低く抑えられるという点で大きなメリットになる。

このDesignStart、2017年には「Cortex-M3」も対象に加えることで、さらに利用できる範囲が広がった。加えてIPサブシステムとして同社のCoreLink SDK-100もDesingStartに含まれることになった。これにより、Cortex-M0よりずっとパワフルなCortex-M3コアに加えてAHB/APBやFlash Cache、RTC、RNGなどのコンポーネントも同時に利用できるようになり、よりIPの初期費用を抑えられるようになった。

ほぼ同じ時期にArmはMbed OSの提供も開始しており、単にSoCの開発費用だけでなく、そのSoC上で稼働するソフトウェア環境の移植も容易かつ低コスト(Mbed OSそのものは無償提供される)になる、という取り組みである。これによって、SoCの開発の障壁をさらに引き下げよう、という試みである。

FPGA上でCortex-M1/M3のIPコアが無償で利用可能に

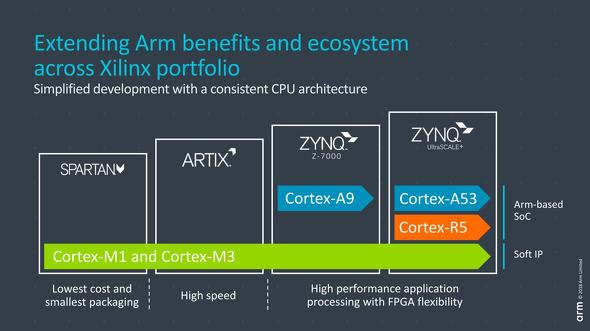

さて、そのDesignStartであるが、2018年は大きく2つのトピックがあった。一つはXilinxのFPGA上でCortex-M1/Cortex-M3のIPコアが無償(ライセンスのみならずロイヤリティーも無償)で利用できるようになったことだ。

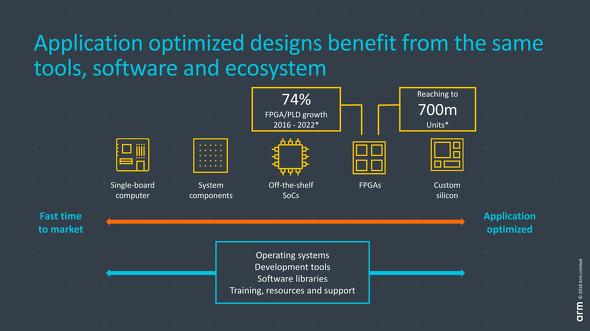

この背景にあるのは、FPGAおよびPLDのマーケットが急速に成長しており、FPGAだけで構成されるシステムが7億ユニットに達する、と見込まれていることがある(図1)。

図1 FPGAは、特に少量多品種向けには非常に有利(デザインコストとかIPコストは変わらないが、何しろマスク製造のコストが掛からないから、初期コストを大幅に抑えられる)というメリットがあり、特にここ数年急速に普及し始めた感がある

図1 FPGAは、特に少量多品種向けには非常に有利(デザインコストとかIPコストは変わらないが、何しろマスク製造のコストが掛からないから、初期コストを大幅に抑えられる)というメリットがあり、特にここ数年急速に普及し始めた感があるFPGAメーカー各社はこうしたシステム向けに、「Cortex-A9」とか「Cortex-A53」などの高性能なプロセッサをハードIPとして搭載したFPGAをラインアップしているが、MCU程度のコントローラーに関してはむしろ手付かずであり、中には複数のMCUを搭載し、それぞれで別の処理をさせたいという場合もある。

こうしたニーズに応えるべく、Xilinxの統合開発ツールである「Vivado」にCortex-M1/Cortex-M3のIPを統合することで、Vivadoが動作するXilinxのFPGAならどれでも、Cortex-M1/M3が無償で利用できるようになった(図2)。

これによって、XilinxのFPGAを使いながらも、Cortex-Mに対応したソフトウェア環境をそのまま利用できるというのは、特にソフトウェア開発の観点で大きなメリットとなる。ちなみにCortex-M1は、Cortex-M0のFPGA対応版(というか、実は先に作られたのがCortex-M1で、これをSoC向けにしたのがCortex-M0)であり、機能的にはCortex-M0とほぼ同じである。こうしたコアを利用できるようになったことで、FPGAだけのシステムで、Armのソフトウェアエコシステムを利用しやすくなった、というのが最初のトピックである。

Cortex-A5もDesignStartの対象に

そして2つ目のトピックが本題である、「Cortex-A5」のサポートである。Cortex-M0/M1/M3はいずれも分類としてはMCUである。何をもってしてMCUとするかというと、Armの定義で言えば仮想記憶に対応したMMU(Memory Management Unit)を搭載していない(MPU(Memory Protection Unit)は搭載される)ことだ。

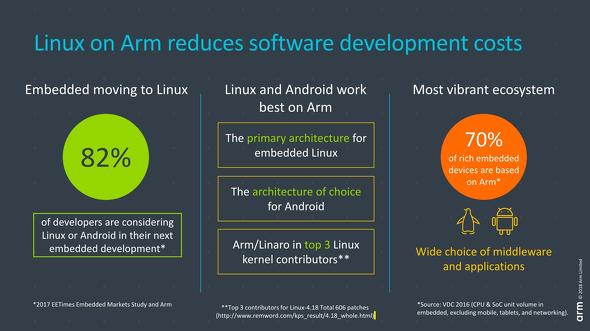

このため、RTOSなどは実行することはできるが、Embedded Linuxなどの仮想記憶に対応したOSは稼働できない。その一方で、組み込みシステムは全般的にEmbedded LinuxあるいはAndroidにシフトしつつあるという状況があり(図3)、カスタムSoCを開発する場合、そのSoCはLinuxあるいはAndroidベースのシステムとして稼働する可能性が非常に高くなってきた。ということは必然的にSoCも、MMUを搭載したArmのCortex-Aシリーズを利用するケースが増えてきている。ただし、ここでまた冒頭の初期コストの問題が発生するわけだ。

図3 ちなみにArmはLinaroと合わせて、Linux KernelのコントリビュータのTop 3に入るほど、Linuxに対しての投資を行っており、事実主要なLinuxのDistributionはArmのアーキテクチャに完全対応している

図3 ちなみにArmはLinaroと合わせて、Linux KernelのコントリビュータのTop 3に入るほど、Linuxに対しての投資を行っており、事実主要なLinuxのDistributionはArmのアーキテクチャに完全対応しているそこで今回Armが発表したのは、Cortex-A5をDesignStartの対象に含むという決断である。Cortex-A5コアは2009年に発表されたもので、構成はシングルパイプライン、インオーダーの比較的シンプルなものである。とはいえ、発表当初はスマートフォン向けのSoCなどにも利用されていたものだから、組み込み機器の制御には十分なパフォーマンスがある。それもあって途中からは組み込み機器向けのアプリケーションプロセッサとしても広く利用されるようになり、既に通算で20億個ほどの出荷台数があるIPコアである。これだけ広範に利用されていれば、もちろん、ソフトウェアの対応も十分である。

初期費用を2段階に設定

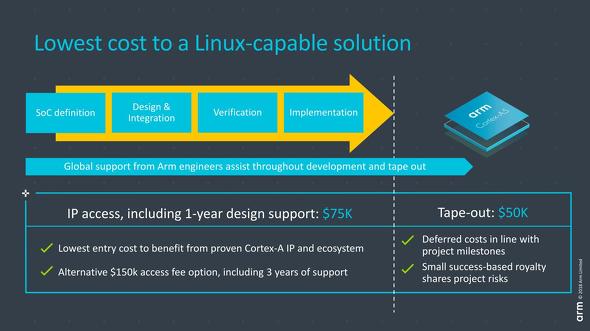

ただし、さすがにCortex-M0/M3と比べると大規模なIPだけに、無償というわけにはいかず、初期費用は合計で12万5000米ドル(または20万米ドル)となった(図4)。もっとも、通常のプロセッサIPと比べるとこれは大幅なディスカウントであることは間違いない。面白いのは、この初期費用が、IPアクセス+テクニカルサポートの7万5000米ドル(または15万米ドル)と、テープアウト後の5万米ドルの2つに分けられていることだ。

本来これは一つの値段になっているものだが、仮に設計を開始したものの、さまざまな理由で設計が中止になってしまうこともしばしばある。値段が一つの場合、設計を中止すると、初期費用の12万5000米ドルなり20万米ドルなりが、まるまる無駄になってしまうが、Design Startでは価格を2つに分割したことで、仮に設計を開始したものの、途中で中断してテープアウトに至らなかった場合、無駄になる金額は7万5000米ドル(または15万米ドル)だけで済む。

大企業の場合、5万米ドルはエンジニア5人月分のコストでしかないが、スタートアップ企業ではこの5万米ドルですら惜しいという場合が少なくない。そうしたスタートアップ企業のリスクを低減するために費用を2分割した、という話である。

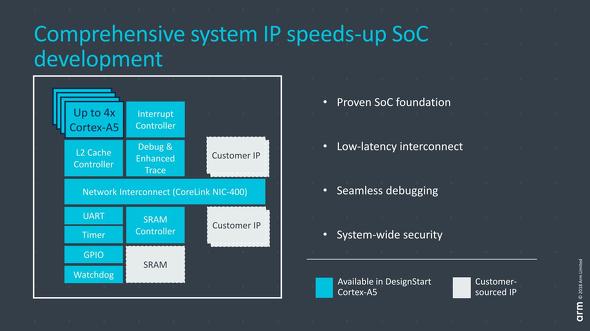

ちなみに、この初期費用にはCortex-A5のコアのみならず周辺回路やインターコネクト、デバッグインタフェースまでが含まれる(図5)。

図5 水色が今回のIP Accessで提供される範囲。SRAMはファウンダリーが提供するSRAMコンパイラが利用できるので、結局各顧客が自身で作るCustomer IPだけを作り、NIC-400につなげれば、あとは全部Armから提供されるもので賄えることになる

図5 水色が今回のIP Accessで提供される範囲。SRAMはファウンダリーが提供するSRAMコンパイラが利用できるので、結局各顧客が自身で作るCustomer IPだけを作り、NIC-400につなげれば、あとは全部Armから提供されるもので賄えることになるCPUコア単体として考えればやや高いと思われるかもしれないが、ここまでのIPを全部込みにしての値段と考えれば、破格と評しても過言ではないお値段として良いと思う。そして図4のタイトルにもあるように、この構成でEmbedded Linux(あるいは、移植作業は必要だろうがAndroid)が稼働するわけで、既にあるEmbedded Linuxベースのシステムの稼働は基本的にはそう難しくない。あるいは新規にソフトウェアを開発するにしても、Embedded Linuxベースのミドルウェア類が利用できるから、相対的に開発は容易である。

ArmのPortfolio Product Management担当ディレクターを務めるPhil Burr氏によれば、「SoCの開発コストと言えば、ハードウェアに目が行きがちだが、トータルコストで言えばソフトウェア開発の比重が非常に大きい。DesignStart Cortex-A5を使うことで、Armのソフトウェアエコシステムを利用可能になり、ここのコストを大幅に抑えられる」とする。

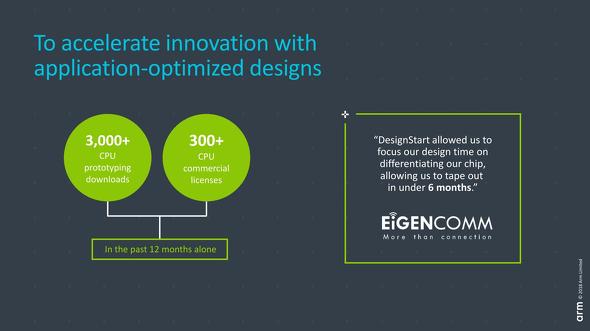

IP accessには1年あるいは3年のデザインサポートが付属しているが、公表されている例で言えば、EiGENCOMMはCPU実装の経験が全くなかったにもかかわらず、デザインサポートの力を借りることで6カ月という短期間でテープアウトしたという実績がある(図6)。

誰でも6カ月でテープアウトまでたどり着けるわけではないが、こうした例を見れば、1年というデザインサポートの期間は決して短いものではないと考えられる。Cortex-A5だと多少難易度は上がると思われるが、それに備えてオプションで3年というサポートも提供される。この辺りは、SoC作りに長けたArmの経験が生きている部分であろう。

図6 過去12カ月で、「DesignStart」経由で評価版が3000以上ダウンロードされ、300社以上が商用版ライセンスを取得している。もっとも、これはCortex-M0/M3を対象とした話なので、Cortex-A5だと、話は多少違ってくるかもしれない

図6 過去12カ月で、「DesignStart」経由で評価版が3000以上ダウンロードされ、300社以上が商用版ライセンスを取得している。もっとも、これはCortex-M0/M3を対象とした話なので、Cortex-A5だと、話は多少違ってくるかもしれないこのように、DesignStartを使うことで、SoC開発の初期費用のうち、設計とIP入手に関わる部分のコストを大幅に抑えやすくなる。

では、マスクコストなどについてはどうだろうか。実は、これもノウハウがある。Burr氏によれば、「SoC製造は高価だと考えられているかもしれないが、そんなことはない。もちろん、最新の7nmプロセスを適用するといった場合は、コストは非常に高くつく。だが、そもそもCortex-A5を利用するプロセスはそれほど最新のプロセスである必要はなく、コストははるかに抑えられる上に、きちんと差別化もできる」とする。これに関する詳細は、"Custom Chips for Dummies 日本語版"(電子書籍)として、Armから無償で配布されている。興味のある方は、ぜひお読みいただきたい。

Copyright © ITmedia, Inc. All Rights Reserved.

提供:アーム株式会社

アイティメディア営業企画/制作:EE Times Japan 編集部/掲載内容有効期限:2018年12月31日

ArmのPhil Burr氏

ArmのPhil Burr氏