従来比20倍のランダム読み出し速度を実現! 高速I/F品の登場で車とともに飛躍が期待されるNORフラッシュ:インフィニオンがLPDDR4対応NORを間もなく量産へ

ADAS(先進運転支援システム)の進化には車載マイコンや車載SoCの高性能化が急務であり、微細半導体製造プロセスを用いたマイコン/SoCの開発が加速している。ただ、微細プロセスではマイコン/SoCに不揮発性メモリを混載するのが難しく、不揮発性メモリを外付けする必要が生じる。だが従来の不揮発性メモリのインタフェース(I/F)では速度が不足し、高速な処理に対応できない。そうした中で、従来比20倍のランダムリードアクセスを実現する高速I/Fを搭載したNOR型フラッシュメモリが登場した。

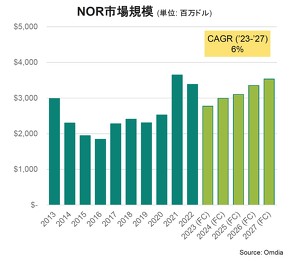

再び市場規模が拡大しつつあるNOR型フラッシュメモリ

NOR型フラッシュメモリ(以下、NORフラッシュ)の市場規模が拡大基調に転じて、今後も成長が期待されていることをご存じだろうか。

ランダムリードが得意でデータ保持期間が極めて長いNORフラッシュは、その特徴から携帯電話機のプログラム格納用メモリとして2000年代に市場規模のピークを迎えた。その後、プログラム容量が大きいスマートフォンの普及に伴い、低容量のNORフラッシュは大容量のNAND型フラッシュメモリとDRAMに置き換えられ、市場規模は縮小していった。

携帯電話機/スマートフォンのプログラム格納メモリの座を奪われたNORフラッシュは、2010年代後半から再び市場規模が拡大傾向に転じている。小型、低消費電力、そして高信頼という特徴が評価されてノイズキャンセリング機能を搭載した完全ワイヤレスイヤフォンの多くにNORフラッシュが採用されている他、自動車用途での利用も拡大しているのだ。

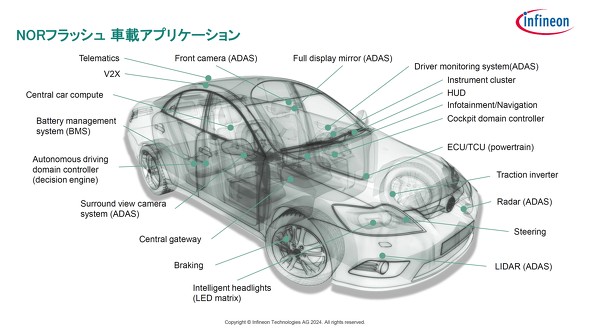

ADAS/自動運転でマイコン/SoCにメモリを内蔵できない時代に

自動車でのNORフラッシュ採用拡大の背景には、先進運転支援システム(ADAS)の普及がある。ADASでは、自動車の周囲を監視するカメラによる画像認識システムが搭載される。画像認識は大量のデータを処理する必要があり、画像を処理する車載SoCや車載マイコンの内蔵メモリだけでは容量が足りず、NORフラッシュを外付けして補完するという需要が拡大している。

自動運転などを実現するために車載SoCや車載マイコンの高性能化が求められる中で、5〜14nmという微細プロセスを用いた車載SoCや車載マイコンが登場しつつある。こうした20nmを下回る微細プロセスでは、製造技術が確立されていない従来のフラッシュメモリを内蔵できない。MRAM(磁気抵抗メモリ)やPCM(相変化メモリ)など、微細プロセスに対応する新たな不揮発性メモリを内蔵する動きも一部あるが、製造コストや容量といった課題があり、外付けメモリに頼らざるを得ない状況になっている。

車載SoCや車載マイコンに書き換え可能な不揮発性メモリを搭載できない時代を迎えて外付けメモリが不可欠になろうとしている中で、ランダムリードが速くてデータ保持期間が長く、自動車に求められる品質を満たすNORフラッシュに期待が集まり、一層の需要拡大が見込まれている。

しかし、NORフラッシュも微細プロセスを採用した高性能車載SoC/マイコンの外付け不揮発性メモリとしての要件を全て満たしているわけではない。内蔵フラッシュほどのデータ転送速度を持つ高速インタフェース(I/F)がないのだ。現状のNORフラッシュのI/FはSPI(Serial Peripheral Interface)を複数本使用したeXpanded SPI(xSPI)が主流で、8本のSPIを使用したxSPIでもデータ転送速度は400Mバイト/秒にとどまる。この値は従来の内蔵フラッシュの転送速度よりも遅く、さらに高速な処理が必要な微細プロセス採用車載SoC/マイコンでは致命的に速度が不足することになる――。

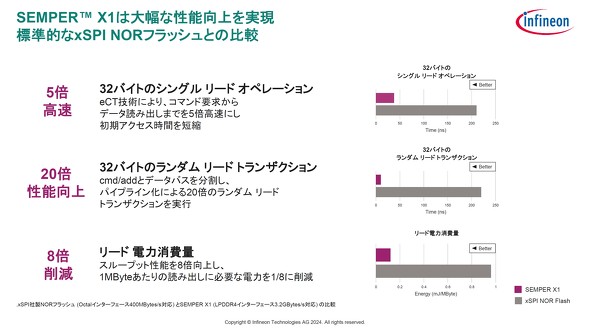

データ転送速度8倍、ランダムリード速度20倍のNORフラッシュの登場

NORフラッシュのI/Fの大幅な高速化が求められる中で、インフィニオン テクノロジーズは従来比8倍に相当する3240Mバイト/秒のデータ転送速度を持つI/Fを採用したNORフラッシュ「SEMPER X1」を開発し、2024年9月末までに量産出荷を始める予定だ。

SEMPER X1は、プログラムコード格納メモリとして最も重要視される読み出し速度を高速化するため、読み出し用I/FにDRAMで用いられるI/F規格「LPDDR4」を採用した。LPDDR4はコマンド/アドレスバスとデータバスが多重化しているSPIと異なり、コマンド/アドレスバスとデータバスが独立してそれぞれが同時に通信できる。そのため、xSPIに対してランダムリード速度が20倍速い。

*)インフィニオンのメモリ事業

2020年に経営統合したCypress Semiconductorが手掛けたメモリ事業を継続して展開。SRAMや不揮発SRAM(nv-SRAM)、F-RAMの他、Cypressが2015年に買収したSpansion(スパンション:AMDと富士通の合弁会社として発足)のNORフラッシュを手掛ける。

LPDDR4の高速性を生かすため、NORフラッシュのメモリ自体の改良も実施。40nm製造プロセスを導入するとともにランダムアクセス性能を高めるべく、旧Spansion時代*から定評のあるチャージトラップ(CT)方式のメモリセル構造を改良した「eCT」(Embedded Charge Trap)を採用。コマンド要求からデータ読み出しまでを従来のxSPI NORフラッシュの5倍に高速化した。インフィニオン テクノロジーズ メモリーソリューションズ プロダクトマネジメント シニアマネージャーを務める品田唱秋氏は「読み出し速度をxSPI NORフラッシュの8倍に速めたことで、データ当たりの読み出しに必要な消費電力も8分の1に削減できる」とし、さまざまな面で従来のxSPI NORフラッシュから飛躍的に進化した。

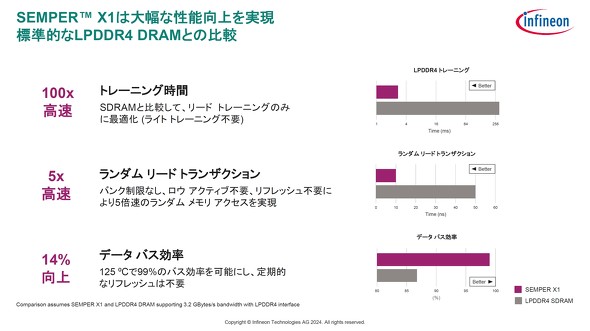

LPDDR4 DRAMを超える読み出し性能

読み出しI/FにLPDDR4を採用したSEMPER X1は、LPDDR4を用いたDRAM(SDRAM)と比べてもさまざまな優位性がある。NORフラッシュはメモリの特性上、DRAMのようなバンク制限がなく、ロウアクティブ、リフレッシュといった処理も不要であり、「ランダムリード速度はDRAMの5倍」(品田氏)とする。リフレッシュが不要なので、SEMPER X1は125℃という過酷な環境下でも99%のバス効率を維持できるというメリットもある。書き込み時のリードトレーニングも不要であり、トレーニング時間もDRAMの100分の1で済む。SEMPER X1は読み出しにおいてLPDDR4 DRAMさえもはるかにしのぐ性能を有しており、プログラムコード格納用に最適なメモリに仕上がっていることが分かる。

なお、SEMPER X1への書き込みについては従来のSPI経由になる。「プログラムコードの書き換え頻度はそこまで高くなく、高速化する必要性はあまりない」とし、読み出し速度の向上に特化した、割り切った性能になっている。「OTA(Over The Air)などを介したプログラムコードの書き換えでは、速度よりもメモリバンクを複数持ち、既存のプログラムコードを走らせながら新たなプログラムを確実に書き込む『ダウンタイムゼロ』への対応が求められる。SEMPER X1は最大576Mビット容量で、16のメモリバンクを備える。用途によっては、現行プログラムと1つ前の世代のプログラム、そして更新用プログラムと、3世代のプログラムを格納するためのメモリバンクを確保することもできる」とし、車載領域での書き込みニーズに適した仕様になっている。

品質、安定供給……自動車市場ニーズにも応える

インフィニオン テクノロジーズは、SEMPER X1として576Mビット容量品の他、288Mビット容量品を用意し、エンジニアサンプルを提供している。量産は2024年9月末までに実施する計画だ。いずれの製品も機能安全規格「ISO 26262」における自動車安全水準「ASIL-B」に準拠し、「ASIL-D」に対応可能になっている。

SEMPER X1は、LPDDR4およびxSPIのI/Fを持つSoCやマイコンで使用できるが「リフレッシュや書き込み時のトレーニングが不要なので、それらの処理を省いたLPDDR4のI/Fで使用することでSEMPER X1の性能を引き出せる」という。SEMPER X1、LPDDR4フラッシュに最適化されたI/Fを持つ車載用プロセッサとして既にNXP Semiconductorsが「S32Z」「S32E」を発表するなど、対応デバイスも登場している。

インフィニオン テクノロジーズは、SEMPER X1のI/Fの規格化を目指して半導体関連技術の標準化団体「JEDEC」に提案し、LPDDR4フラッシュの仕様策定を進めているという。品田氏は「もともとはわれわれの独自I/FだったxSPIと同様、LPDDR4フラッシュについても標準化して自動車市場で要求されるマルチソースを実現する環境を整える」とする。

その上で「安定供給のための投資を継続する。NORフラッシュの製造拠点は中国や台湾といったアジア地域に集中している。当社は米国テキサス州の自社工場と中国の委託工場の2カ所でNORフラッシュを生産しており、地政学的なリスクを軽減できている数少ないNORフラッシュメーカーでもある。技術、品質、安定供給などあらゆる面で自動車市場のニーズに応え、今後拡大が予想される車載メモリ需要に対応する」としている。

Copyright © ITmedia, Inc. All Rights Reserved.

提供:インフィニオン テクノロジーズ ジャパン株式会社

アイティメディア営業企画/制作:EE Times Japan 編集部/掲載内容有効期限:2024年4月26日

インフィニオン テクノロジーズ メモリーソリューションズ プロダクトマネジメント(Flash Solution)シニアマネージャー 品田唱秋氏

インフィニオン テクノロジーズ メモリーソリューションズ プロダクトマネジメント(Flash Solution)シニアマネージャー 品田唱秋氏