【VLSI 2010】東芝、16nm以降で役立つナノワイヤトランジスタを高性能化:プロセス技術

東芝は、16nm以降の製造技術を適用したシステムLSIで必要になると見られる、ナノワイヤトランジスタの性能向上に成功した。

東芝は、寄生抵抗を低減し、オン電流を従来と比べて75%高めたことで、ナノワイヤトランジスタとしては世界トップレベルとなる1mA/μmのオン電流を実現したと主張する。同社は、2010年6月15日〜17日に米国ハワイ州で開催された半導体デバイスに関する国際会議「2010 Symposia on VLSI Technology and Circuits」でこの技術を発表した。

プレーナ型トランジスタを微細化していくと、オフ時のリーク電流が問題となることはよく知られている。この問題を解消するために東芝が採用したのが立体構造トランジスタだ。立体構造トランジスタは、FinFETと同様に、トランジスタのチャネル部をゲートで3方向から取り囲むことで、ゲート面積を大きくする。

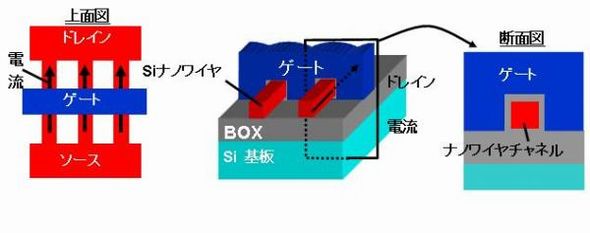

ナノワイヤトランジスタ(図1)は立体構造トランジスタの一種で、細いワイヤ形状のSi(シリコン)チャネル(ナノワイヤチャネル)をゲートで取り囲む構造になっており、短チャネル効果によるオフ時のリーク電流を抑制できる。しかし、ソースやドレインとゲートの間にある絶縁層(ゲート側壁)の下の領域で寄生抵抗が増大し、オン電流が低下するという課題があった。

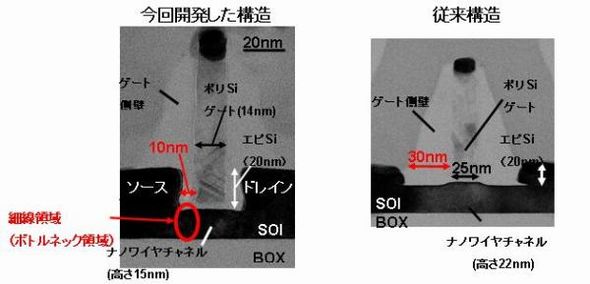

東芝は、この課題に対処するために、ゲート側壁加工を改良し、30nmあったゲート側壁の厚さを10nmにまで薄くした(図2)。また、ソース・ドレイン電極上にSiをエピタキシャル成長させることで、寄生抵抗を低減し、オン電流を40%向上させることにも成功した。同社はさらに、チャネル部分のシリコン層の結晶方位を従来の(110)面方向から45度回転させた(100)面方向に変更することで、オン電流を25%向上させた。

こうした成果により、東芝はオフ電流100nA/μmで、オン電流を従来と比べて75%向上させ1mA/μmの電流量を実現した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- AIの競争軸は半導体から電力へ――日本の戦略の「死角」に

- ロームとデンソー、東芝、三菱電機……国内パワー半導体再編の行方

- NVIDIA製GPU搭載サーバのコスト/スペックを分析してみた

- ダイヤモンドMOSFETで初の200V、1AのSW動作を達成

- ロームと東芝、半導体事業の提携強化へ「協議を継続中」

- JDI、車載ディスプレイ事業分割を中止「中長期的に最善」

- 「NVIDIAとGroqの取引」がAI新興にもたらした2つの効果

- カメラベースで雪道をハンズオフ走行、SUBARUとInfineon協業の意義

- AI/HPCシステムのメモリ/ストレージ階層とHBMの高性能化

- ローム、デンソーによる買収提案は「事実」

図1 ナノワイヤトランジスタの構造

図1 ナノワイヤトランジスタの構造 図2 従来のナノワイヤトランジスタと、今回開発に成功した新構造のナノワイヤートランジスタ

図2 従来のナノワイヤトランジスタと、今回開発に成功した新構造のナノワイヤートランジスタ