AI/HPCシステムのメモリ/ストレージ階層とHBMの高性能化:福田昭のデバイス通信(510) TSMCが解説する最新のパッケージング技術(7)(1/2 ページ)

「IEDM 2025」におけるTSMCの講演内容を紹介する。今回は「(2)Memory bandwidth scalability(メモリ入出力帯域幅の拡張性)」を取り上げる。

メモリ帯域幅の拡張が必須であるAI/HPCシステム

2025年12月に開催された国際学会IEDMのショートコース(技術解説)で、シリコンファウンドリー最大手のTSMCが最新のパッケージング技術を説明した。講演のタイトルは「Advanced Packaging and Chiplet Technologies for AI and HPC Applications(AIおよびHPCに向けた先端パッケージング技術と先端チップレット技術)」、講演者はAdvanced Package Integration Division R&DのディレクターをつとめるJames Chen氏である。大変に参考となる内容だったので、その一部をシリーズでご紹介している。ただし講演内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演内容を筆者が適宜、補足してある。あらかじめご了承されたい。

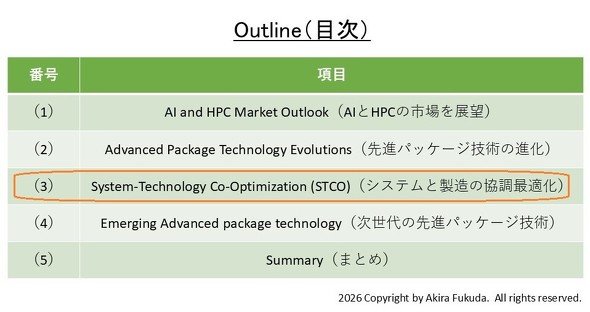

講演「Advanced Packaging and Chiplet Technologies for AI and HPC Applications(AIおよびHPCに向けた先端パッケージング技術と先端チップレット技術)」のアウトライン[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

講演「Advanced Packaging and Chiplet Technologies for AI and HPC Applications(AIおよびHPCに向けた先端パッケージング技術と先端チップレット技術)」のアウトライン[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)タイトルスライドの次に示されたアウトラインは、「AI and HPC Market Outlook(AIとHPCの市場を展望)」「Advanced Package Technology Evolutions(先進パッケージ技術の進化)」「System-Technology Co-Optimization (STCO)(システムと製造の協調最適化)」「Emerging Advanced package technology(次世代の先進パッケージ技術)」「Summary(まとめ)」となっていた。

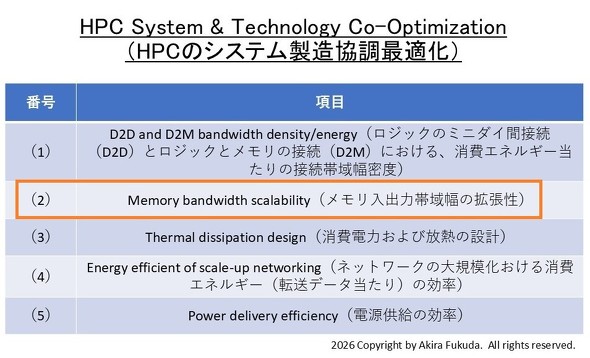

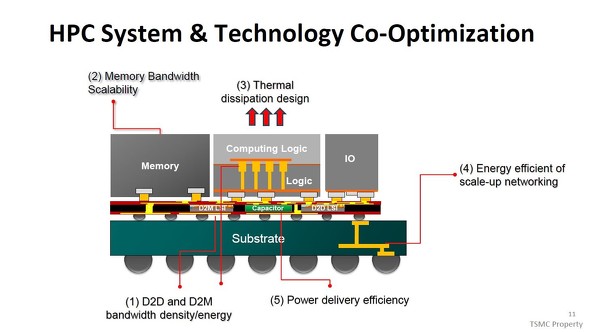

本シリーズの前々回では、アウトラインの第3項「System-Technology Co-Optimization (STCO)(システム・製造協調最適化)」に相当する部分の説明に入った。前回は先進パッケージ「CoWoS-L(LSI+RDL interposer)」を例に、STCOで考慮すべき5つの項目を順番にご報告し始めた。

具体的には、最初の項目「(1)D2D and D2M bandwidth density/energy(ロジックのミニダイ間接続(D2D)とロジックとメモリの接続(D2M)における、消費エネルギー当たりの接続帯域幅密度)」を前回でご説明した。今回は2番目の項目「(2)Memory bandwidth scalability(メモリ入出力帯域幅の拡張性)」を簡単に述べたい。

STCO(システムと製造の協調最適化)で考慮すべき事柄。先進パッケージ「CoWoS-L(LSI+RDL interposer)」の例[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

STCO(システムと製造の協調最適化)で考慮すべき事柄。先進パッケージ「CoWoS-L(LSI+RDL interposer)」の例[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)遅延時間/帯域幅と記憶容量のトレードオフ

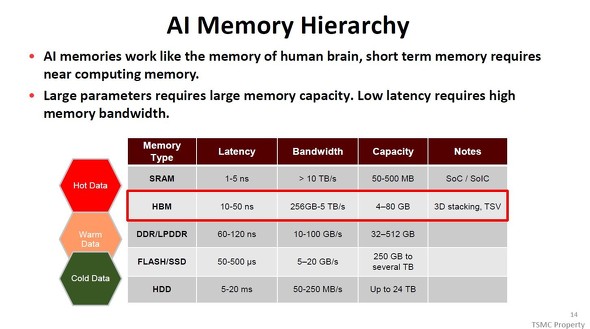

始めはAI/HPCシステムのメモリ/ストレージ階層を説明しよう。アクセスの遅延時間(Latency)と入出力帯域幅(Bandwidth)、記憶容量(Capacity)の異なる複数のメモリ/ストレージ技術によって構成される。アクセス頻度の高いデータは通常、遅延時間が短く、入出力帯域幅が広いメモリ(速度の高いメモリ)に格納する。最も速度の高いメモリ技術はSRAMである。SRAM技術はプロセッサのレジスタ、1次/2次キャッシュ、タグメモリなどに使われている。

次の速度の高い技術は、DRAMをベースにしたHBM(High Bandwidth Memory)である。ハイエンドのAI/HPCシステムではHBMが主記憶(メインメモリ)に使われる。その次がDDR/LPDDR DRAM技術となる。ハイエンドのAI/HPCシステムでは第2階層の主記憶、ミッドレンジのAI/HPCシステムでは第1階層の主記憶にDDR/LPDDR DRAMが使われる。

さらにその次は、ストレージ技術を利用する。NANDフラッシュメモリを記憶媒体として内蔵したSSD(Solid State Drive)がストレージの第1階層である。磁気ディスクを記憶媒体として内蔵したHDD(Hard Disk Drive)がストレージの第2階層となる。

メモリ/ストレージ階層では速度(遅延時間および帯域幅)と、記憶容量がトレードオフ関係にある。高速のメモリ技術は記憶容量が小さい。記憶容量が大きなメモリ技術(およびストレージ技術)は、速度が低い。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- メモリも中国が猛追 YMTCは新工場建設

- 560億ドル投資でも「需要に追い付けない」 AI急成長でTSMC表明

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- 「AI特需」の恩恵届かぬ日本企業 Gartnerが見る2026年半導体市場

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- SAIMEMORYの垂直ビルド構造メモリ開発がNEDO採択

- 「Rapidusの隣」に光電融合パッケージ開発拠点、28年度の完成目指す

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- データセンター用CPUでも勢力伸ばすRISC-V