アルテラのStratix10、新アーキテクチャ採用で従来比2倍のコア性能:FPGA(1/2 ページ)

アルテラは、ハイエンドのプログラマブルロジックデバイス「Stratix10FPGA&SoC」のアーキテクチャと製品概要を発表した。新製品は「HyperFlexアーキテクチャ」や「ヘテロジニアス3D SiP(System in Package)インテグレーション」技術を採用している。製造はIntelの14nmトライゲートプロセスを用いて行われる。

アルテラは2015年6月9日、ハイエンドのプログラマブルロジックデバイス「Stratix10FPGA&SoC」のアーキテクチャと製品概要を発表した。Intelの14nmトライゲートプロセスを用いて製造される新製品は、「HyperFlexアーキテクチャ」や「ヘテロジニアス3D SiP(System in Package)インテグレーション」技術を採用することで、高い性能と電力効率、拡張性、柔軟性を実現している。

アルテラは「Generation10」製品群として、既にミッドレンジ製品の「Arria 10」と、低コスト製品の「MAX 10」を発表している。今回詳細を明らかにしたStratix10は、高速/高集積なハイエンド製品に位置付けられている。エンジニアリングサンプル品の出荷開始は2015年第4四半期(10〜12月)の予定だ。

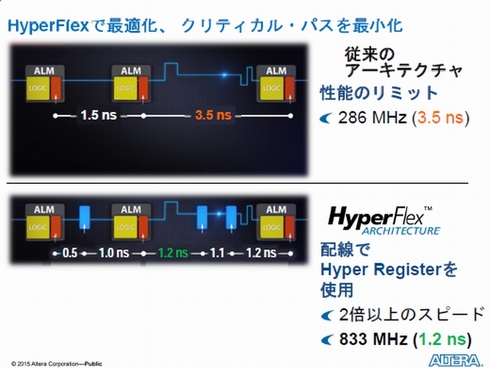

Stratix10FPGA&SoCは、「HyperFlex」と呼ぶアーキテクチャを採用した。全てのコア・インタコネクト配線セグメントに「ハイパーレジスタ」を搭載している。これによって、チップの性能向上でボトルネックとなっていた配線遅延を極めて小さくすることができるという。

従来FPGAのアーキテクチャでは、ロジックアレイブロック内にあるアダプティブロジックモジュール(ALM)間の信号転送に最大3.5ns(286MHz相当)の遅延が生じていた。HyperFlexアーキテクチャは、こうした配線遅延の課題を解決した。ALM間を接続する配線途中にハイパーレジスタを挿入することによって、クリティカルパスを最小化し、配線による遅延時間を最大1.2ns(833MHz相当)に抑え込むことができた。14nmトライゲートプロセスとの組み合わせにより、従来アーキテクチャに比べて2倍以上のコアロジック性能を実現できるという。

アルテラでプロダクトマーケティングのシニアディレクタを務めるPatrick Dorsey氏は、「100社以上のアーリーカスタマがStratix10FPGA&SoCを評価中だが、光伝送やワイヤレス通信インフラ装置の用途では、従来製品に比べて2倍の性能を達成しているとの情報を聞いている」と話す。

新たなアーキテクチャの採用などにより、高い性能を実現できたことから、最大70%の消費電力を削減することが可能になるという。必要以上にバス幅を広げなくても十分な性能が得られ、ロジック面積も節減することができるためだという。「データセンタに設置されるサーバへの応用例では、現行FPGAを5個使用していたため、チップの消費電力は120Wに達していた。Stratix10FPGA&SoCを用いると、同じ性能を1個のチップで実現できるため44Wで済む」(Dorsey氏)ことから、消費電力を大幅に削減できると話す。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

- パワー停滞も光デバイス堅調、三菱電機の半導体部門

Stratix10FPGA&SoCのチップイメージ

Stratix10FPGA&SoCのチップイメージ

アルテラでプロダクトマーケティングのシニアディレクタを務めるPatrick Dorsey氏

アルテラでプロダクトマーケティングのシニアディレクタを務めるPatrick Dorsey氏