アルテラのStratix10、新アーキテクチャ採用で従来比2倍のコア性能:FPGA(2/2 ページ)

ヘテロジニアス3D SiPインテグレーション技術

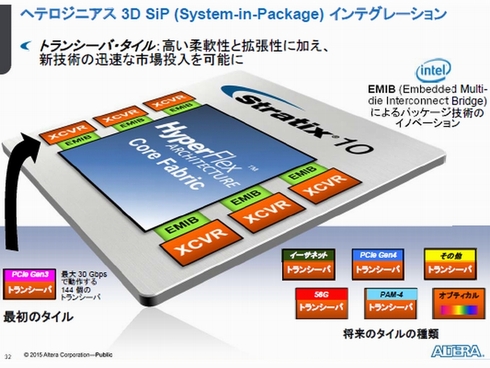

Stratix10FPGA&SoCで採用したもう1つの技術が、ヘテロジニアス3D SiPインテグレーション技術である。最大5.5M ロジックエレメント(LE)相当のロジックを集積したFPGAコアファブリックとそれ以外の複数チップを、1つのパッケージに集積することができる。

ヘテロジニアス3D SiPインテグレーションには、Intel独自のEMIB(Embedded Multi-die Interconnect Bridge)技術が用いられている。インタポーザベースの接続手法に比べて、性能を向上でき、実装の簡素化やコスト削減、信号品質を向上することが可能となる。

さらに、EMIB技術を活用することで、トランシーバの技術進化にも柔軟に対応することができるという。新技術では、仕様変更にも迅速に対応できるよう、「タイル」と呼ぶ概念を導入した。現在、PCIe Gen3に対応するトランシーバのタイルをハードIPで提供している。それ以外の最新規格については当面ソフトウェアIPで対応することになるが、標準規格として確定すれば、PCIe Gen4や56G、PAM-4などに対応するトランシーバのタイルも、ハードIPとして新たに用意していく予定だ。

包括的なセキュリティ機能を搭載

Stratix10FPGA&SoCは、セキュリティ機能も強化した。Athena GroupおよびIntrinsicIDとの協力に基づいて、Stratix10FPGA&SoC向けの高度な暗号化アクセラレーションとPUF(Physically Unclonable Function) IPを用意した。具体的にはセクタ単位の認証と暗号化、多要素認証および、PUF技術に対応したセキュアデザインマネージャ(SDM)のサポートである。これらは、クラウドシステムや防衛関連装置、有線通信装置などでその重要度が高まっているという。

この他、Stratix10ファミリには、最大1.5GHzで動作する64ビットARMクアッドコアCortex-A53がハードプロセッサコアとして搭載される。システムメモリマネジメントユニットや外部メモリコントローラ、高速通信インタフェースなど周辺機能も備えている。さらに、ハードブロックで浮動小数点DSPを搭載しており、単精度演算を最大10TFLOPSの性能で実行することができる。

Stratix10ファミリの特長を最大限発揮させるための開発環境や、デジタル制御方式のDC-DCコンバータICも用意した。「Quartus II」開発ソフトウェアには、新たに「Spectra-Q」エンジンが搭載されている。HyperFlexアーキテクチャが備えているさまざまな性能や機能を最大限に高めつつ、階層設計への対応やコンパイル時間の短縮、高位合成への対応などを実現した。DC-DCコンバータICは、FPGAに内蔵されたSmart VID(Smart Voltage ID)情報を読み取り、供給する電圧をFPGAチップごとに最適化することができる。これによってFPGAの消費電力を節減する仕組みとなっている。

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- ダメ半導体ベンチャーだったLattice SemiconductorのV字復活劇はPLDとともに

- Xilinxの訴訟や3度のIPO延期を耐えたActelは晴れてFPGAベンダーの3位グループに

- 独創的なロジック記憶手法で違いを見せつけたActelはいかにして誕生したのか

- 飛躍するXilinx、AMDとの因縁も既に始まっていた!?

- FPGAを発明したXilinxとセイコーエプソンの知られざる深イイ関係

- レナード・ニモイがAlteraのCPLDを隆盛に導いた!? Xilinxとの競合も始まる

- Alteraの創業によるCPLDの萌芽でプログラマブルロジックはさらなる進化へ

- プログラマブルロジック市場を創り出した「PAL」は逆転のひらめきから生まれた

- プログラマブルロジックの誕生――CPLD前史

関連キーワード

FPGA | アルテラ | 性能 | 3D | 14nmプロセス | Intel | ARM | プログラマブルロジック(エレクトロニクス) | SiP(System in Package)

関連記事

インテルがアルテラを167億ドルで買収へ

インテルがアルテラを167億ドルで買収へ

IntelがAlteraを167億米ドル(約2兆円)で買収する。2015年4月には、買収の交渉が決裂したと報じられたが、その後、合意にこぎつけたようだ。 アルテラが20nm SoC FPGAを出荷開始、性能は50%向上

アルテラが20nm SoC FPGAを出荷開始、性能は50%向上

アルテラは、20nmプロセス技術を用いて製造する第2世代SoC(System on Chip) FPGA「Arria 10 SoC」の出荷を開始した。前世代製品に比べて、処理性能を最大50%向上し、消費電力は最大40%削減できるという。 IntelのAltera買収報道、アナリストらは冷静

IntelのAltera買収報道、アナリストらは冷静

IntelがAlteraに買収を持ちかけている――。複数のメディアがこのように報じたが、業界アナリストらは、この報道に対して冷静な見方をしているようだ。PC市場に比べてFPGA市場は規模が小さく、予想される買収金額の割に、売上高は少ないのではないか、と指摘する声もある。 2つのフラッシュメモリを集積、アルテラが「MAX 10 FPGA」を発表

2つのフラッシュメモリを集積、アルテラが「MAX 10 FPGA」を発表

アルテラは、「Generation 10」製品群として、新たに「MAX 10 FPGA」を発表した。新製品は、2つのコンフィギュレーション用フラッシュメモリブロックやソフトコア「Nios II」プロセッサなどを搭載している。周辺機能を集積することで、同等性能のFPGAに比べて、ボード占有面積を最大50%も節減できるという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

- パワー停滞も光デバイス堅調、三菱電機の半導体部門