プレーナ型NANDフラッシュの微細化の限界:メモリ各社の製品から探る(2/4 ページ)

» 2015年06月23日 09時30分 公開

[Kevin Gibb(TechInsights),EE Times]

ダブルパターニングの2つのアプローチ

ダブルパターニング技術では、2種類のアプローチを適用することができる。LELE(Litho-Etch-Litho-Etch)方式のダブルパターニングは、論理プロセスに適用される場合が多い。もう1つのSADP(Self Aligned Double Patterning)方式は、メモリメーカーで採用されている。ただしこの方式は、 現行の16nmプロセス世代までのNANDフラッシュには効果的だったが、10nmクラスには適さない可能性がある。

それでも今のところ、プレーナ型NANDフラッシュメモリを10nm世代まで微細化することが最も重要な課題だと考えられている。このため、3D NANDフラッシュメモリの開発に向けた取り組みが加速する結果となった。図1では、完全を期すために、SamsungのV-NANDも示してある。また、東芝やSK-Hynix、Micronも近々、3D NAND製品を発表するとみられている。

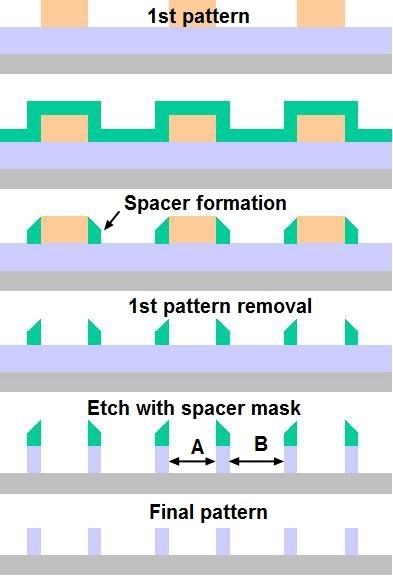

ダブルパターニングは、16nmプロセスのNANDフラッシュの製造に必須の技術になっている。メモリーメーカーは、アクティブコントロールゲートやフローティングゲート、ビット線パターニングにSADPを用いている。図2は、イニシャルパターンの作製から、側壁(サイドウォール)スペーサエッチングを経て、ダブルパターニングに至るまでの、SADPのフローについて図解している。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR

図2 SADPのフロー 出典:Wikipedia

図2 SADPのフロー 出典:Wikipedia