プレーナ型NANDフラッシュの微細化の限界:メモリ各社の製品から探る(3/4 ページ)

» 2015年06月23日 09時30分 公開

[Kevin Gibb(TechInsights),EE Times]

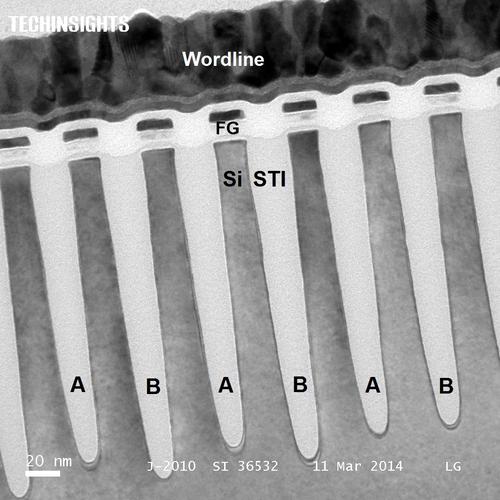

Micronの16nm NANDフラッシュ

ダブルパターニングプロセスでは、サイドウォールスペーサの間隔が均一でない場合もある。これは、ABパターニングと呼ばれ、Micronの16nm NANDフラッシュ(図3)のSTI(Shallow Trench Isolation)パターニングで確認できる。

図3では、シリコンチャネルに整合させたプレーナ型フローティングゲート(浮遊ゲート)上で、左から右にタングステンのワード線が走っている。フローティングゲートとシリコンチャネルは、SADPによって、パターニングとエッチング処理が行われている。隣接するシリコンチャネル間のSTIの下部を見ると、特徴的なABパターニングがエッチングの深さに表れていて、SADPが適用されていることが分かる。

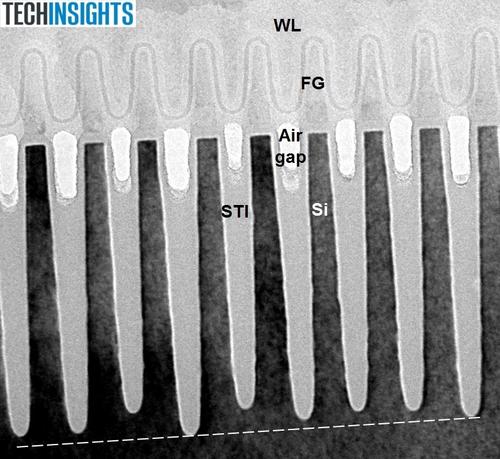

SK-Hynixは、同社の「Middle-1X(M1X)」nm世代のフローティングゲートNANDに、クアッドスペーサパターニングを適用している。同社は、「IEDM 2013」で発表したこの技術を、図4の16nm NANDフラッシュに適用していると思われる。

ただし、トレンチ下部のABパターンは、よりランダムなパターニングになっている。Samsungの16nm NANDフラッシュや東芝の15nm NANDフラッシュにも、これと同様のランダムなパターニングが見られることから、両社がクアッドスペーサパターニングプロセスを適用していると考えられる。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR

図3 Micronの16nm NANDフラッシュの電子顕微鏡画像。シリコンチャネルとSTIを確認できる 出典:TechInsights

図3 Micronの16nm NANDフラッシュの電子顕微鏡画像。シリコンチャネルとSTIを確認できる 出典:TechInsights 図4 SK-Hynixの16nm NANDフラッシュのシリコンチャネルとSTI 出典:TechInsights

図4 SK-Hynixの16nm NANDフラッシュのシリコンチャネルとSTI 出典:TechInsights