進む7nmプロセスの開発、TSMCとIBMが成果を発表:IEDM 2016(1/2 ページ)

米サンフランシスコで開催された「IEDM 2016」では、TSMCとIBMがそれぞれ最新プロセス技術について発表し、会場を大いに沸かせたようだ。

TSMCとIBMの発表に沸いたIEDM

TSMCとIBMは、米国カリフォルニア州サンフランシスコで2016年12月3〜7日に開催された、最先端電子デバイスの研究開発に関する国際学会「IEDM 2016」の初日に、それぞれ7nmプロセス技術に関する論文を発表した。大勢の来場者でにぎわう会場は、まるでクリスマスプレゼントのようなこの発表を受け、大いに活気付いた。両社の論文は、ムーアの法則とEUV(極端紫外線)リソグラフィの両方を前進させる開発成果を明らかにしている。

TSMCは、業界最小となる6T(6トランジスタ) SRAMを開発し、2017年4月までにはリスク生産を開始する予定だという。またIBMは、EUVを適用した研究装置を使用して、業界最小のFinFETを実現したと発表している。

会議の主催者は2016年10月に、これらの論文を、IEDM 2016に関する最新ニュースの見出しとして取り上げている。にもかかわらず、両社は今回、予想をはるかに上回る素晴らしい成果を挙げ、会場を驚かせた。

IBMは、CPP(Contacted Poly Pitch)が44/48nm、金属ピッチが36nm、フィンピッチが27nmのFinFETを発表した。また、ソース・ドレインのコンタクト開口が約10nm、ゲート長が約15nmのデバイスもあるという。

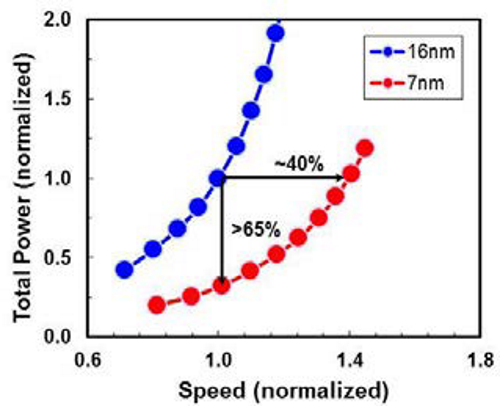

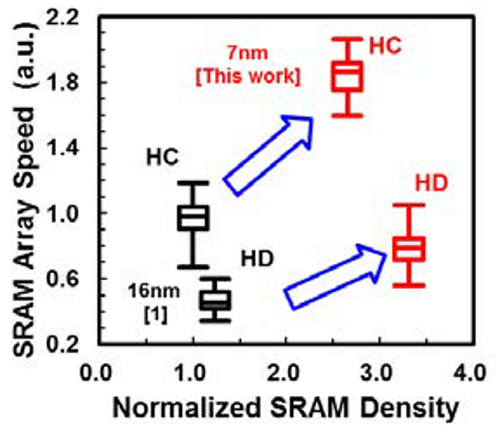

TSMCが発表した256MビットのSRAMテストチップは、セル密度が0.027mm2で、読み出し/書き込み電圧を0.5Vに低減するという。TSMCでN7開発担当シニアディレクターを務めるMichael Shien-Yang Wu氏は、「当社が現在量産を進めている16FF+プロセス技術と比べて、最大40%の高速化と、65%の低消費電力化、3.3倍のルートゲート密度を実現することができる」と述べている。

またWu氏は、7nmプロセスを適用してEUVの有効性を実証する取り組みについても説明しているが、これに関しては、同氏が今回正式に発表した論文の中には記されていない。次世代リソグラフィは、既存の液浸ステッパーに匹敵するフィデリティー(忠実度)と歩留まりを実現することが可能なため、同社は2017年に実用化する予定の7nmプロセスで採用する予定だという。

ASMLのEUV装置は、現在も生産開始前の試作段階にある。TSMCは既に、5nmプロセスでEUVを使用する予定であることを発表している。

Wu氏は、TSMCの7nmプロセスが、同社の10nmプロセスや、Samsung Electronics(サムスン電子)などのライバル企業のプロセス技術と比較してどのように異なるかについては、詳細を明らかにしなかった。また同氏は、TSMCの7nm FinFETのアスペクト比や、7nmプロセスで使用する最新の歪み技術についても詳細な説明は避け、GPUやARMの「Cortex A-72」コアを搭載するテストチップの歩留まりの数値が2桁であることのみを明かすにとどめた。

PC関連技術の記事やホワイトペーパーの発信を手掛ける米国のReal World TechnologiesのアナリストであるDavid Kanter氏は、「TSMCの論文には、7nmプロセスでサポート可能な電圧範囲に関する記述がない。また、エアギャップをサポートしているかどうかを示す顕微鏡写真が、1枚も掲載されていない」と指摘する。

Kanter氏は、「Wu氏が、『7nm SRAMの歩留まりが50%に達した』と述べていることから、2017年後半には量産を開始する予定だとみている」と述べた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- 次世代パワー半導体 「期待の5材料」の現在地

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

TSMCは、同社の「16FF+」プロセスと7nmプロセスの比較結果を発表した 出典:IEDM

TSMCは、同社の「16FF+」プロセスと7nmプロセスの比較結果を発表した 出典:IEDM TSMCの7nm SRAMの記憶密度は新しい次元に達した 出典:IEDM

TSMCの7nm SRAMの記憶密度は新しい次元に達した 出典:IEDM