進む7nmプロセスの開発、TSMCとIBMが成果を発表:IEDM 2016(2/2 ページ)

EUVでプロセスを単純化できる?

IBMの研究者であるHui-Ming Bu氏は、今回の研究成果を受けて、GLOBALFOUNDRIESなど同社のパートナー企業が製造を開始する可能性があるかどうかについては、それほど気にかけてはいないようだ。

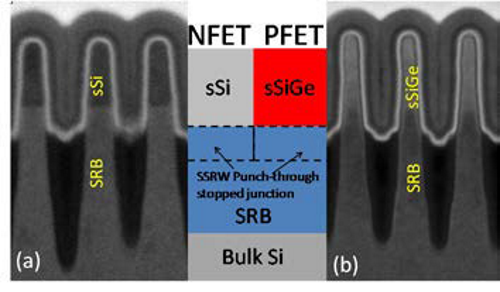

同氏は今回、Si(シリコン)-nFETとSiGe(シリコンゲルマニウム)-pFETを同一基板上で使用し、二重の歪みチャネルを形成するための技術について説明している。

IBMは論文の中で、「M1ラインや最新の金属インターコネクトなど、BEOL(バックエンド)における重要な工程の幾つかにおいてEUVを使用することにより、プロセスの単純化を実現できる」と述べている。

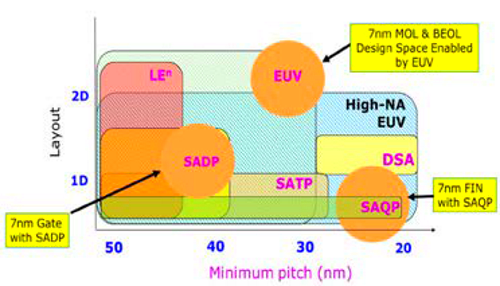

27nmのフィンの製造では、SIT(Sidewall Image Transfer:側壁イメージ転写)技術を2回適用し、自己整合型のクアッドパターニングプロセスを採用したという。IBMは、自己整合型のダブルパターニングを使用してゲートを作成している。

Bu氏は、「トランジスタでは、タングステン(W)ではなくコバルト(Co)を使うことにより、ライン/垂直抵抗を削減できる」と述べる。同氏は、IBMグループの研究がまだ成熟レベルに達しておらず、歩留まりで成果を上げられていないことを認めている。

Kanter氏は、「いずれの論文からも、EUVが製造工場で使われる日が近いわけではないことが分かる。IBMはこれまで長年にわたり、EUVの実用化に向けて積極的に取り組んできた。一方、TSMCは保守的で、IEDM 2016でもEUVに関してあまり楽観視していないような発言をしている」と指摘する。

IntelとSamsungはプロセス技術を発表せず

今回のIEDM 2016では、ライバル同士であるSamsungとIntelが、自社の最先端プロセス技術に関する取り組みを発表することはなかった。Intelは2016年8月に、10nmプロセスにおいてゲートピッチ56nmを達成したと発表しているが、IBMの研究チップは今回、これを上回るピッチを実現し、同プロセスでは業界最高密度を達成したとしている。2017年には製造を開始する見込みだという。

Samsungは最近、10nmプロセスを発表し、「既存の液浸リソグラフィを使用する7nmプロセスをスキップするつもりだ。その代わりに、EUVを使用した7mプロセスを発表し、2018年末までには製造を開始できるとみている」と述べていた。

GLOBALFOUNDRIESは2016年9月に、液浸ステッパーを使用して7nmプロセスを独自開発し、2018年には製造を開始する予定であると発表している。

【翻訳:田中留美、編集:EE Times Japan】

関連記事

「SEMICON West 2016」、imecが展望する5nm世代の配線技術(前編)

「SEMICON West 2016」、imecが展望する5nm世代の配線技術(前編)

imceによる、5nm世代のロジック配線プロセスを展望した講演を、前後編の2回にわたりお届けする。前半では、配線抵抗(R)、配線容量(C)、RC積という配線のパラメータの特徴を紹介する。さらに、10nm世代、7nm世代、5nm世代と微細化が進むと、配線抵抗(R)、配線容量(C)、RC積がどのように変化していくかを解説する。 Samsung、10nm SoCの量産を2016年内にも開始か

Samsung、10nm SoCの量産を2016年内にも開始か

Samsung Electronics(サムスン電子)が10nm FinFETプロセスを適用したSoC(System on Chip)の量産体制を着々と整えているようだ。「Galaxy Note 7」の発火問題で同社のファンドリー事業も停滞するとみられているが、最先端プロセスの実用化に向け、開発を進めている。 次世代Snapdragon、Samsungの10nmプロセスを適用

次世代Snapdragon、Samsungの10nmプロセスを適用

Qualcommは、同社のSoC(System on Chip)「Snapdragon 835」に、Samsung Electronicsの10nmプロセスを適用すると発表した。QualcommはSamsungとの間で、ファウンドリー契約を10年延長している。 Intel、ARM経営幹部をIoT部門トップに任命

Intel、ARM経営幹部をIoT部門トップに任命

Intelが、同社のIoT(モノのインターネット)部門のトップにARMの元経営幹部を任命した。他にも自動車事業グループのトップにDelphi Electronics & Safetyの人物を任命するなど、IntelはIoTおよび車載事業を強化する上で戦略的な人事を行っている。 IBMが7nm試作チップを発表、Intelに迫る勢い

IBMが7nm試作チップを発表、Intelに迫る勢い

IBM Researchが、EUV(極端紫外線)リソグラフィとSiGe(シリコンゲルマニウム)チャネルを使用した7nmプロセス試作チップを発表した。IBM Researchはここ最近、最先端プロセスの研究開発成果の発表に力を入れていて、7nmプロセスの技術開発に自信を示してきたIntelに迫る勢いを見せている。 人間の脳が握る、デバイス低消費電力化の鍵

人間の脳が握る、デバイス低消費電力化の鍵

ウェアラブル機器に欠かせない要件の1つに、低消費電力がある。「第2回 ウェアラブルEXPO」のセミナーに登壇した日本IBMは、超低消費電力のコンピュータとして、人間の”脳”を挙げ、IBMが開発中の「超低消費電力脳型デバイス」について語った。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- 全固体電池の製造プロセス簡素化、東北大が新手法

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

IBMの研究では、SiとSiGeのチャネルを組み合わせている

IBMの研究では、SiとSiGeのチャネルを組み合わせている IBMが開発している7nmプロセスでは、3種類のパターニング技術が使われている

IBMが開発している7nmプロセスでは、3種類のパターニング技術が使われている