量子チップ向けの低雑音評価システム:エヌエフ回路設計ブロックが展示

エヌエフ回路設計ブロックは、2020年10月28〜30日に幕張メッセで行われた「第1回 量子コンピューティングEXPO」で、量子コンピュータチップの評価向けに、低雑音を特長とする信号処理ソリューションを展示した。

エヌエフ回路設計ブロックは、2020年10月28〜30日に幕張メッセで行われた「第1回 量子コンピューティングEXPO」で、量子コンピュータチップの評価向けに、低雑音を特長とする信号処理ソリューションを展示した。

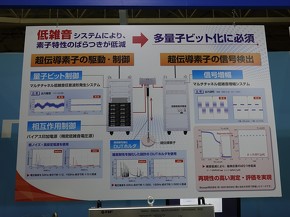

同ソリューションは、量子アニーリング方式のコンピュータシステムにおいて、超伝導素子の制御や信号検出を高精度に行うためのシステム。超伝導素子の駆動/制御ユニットと、超伝導素子の信号検出ユニット、そして超伝導デバイスを装着するDUT(Device Under Test)ホルダーから構成される。DUTホルダーに、評価対象となるチップを装着し、それを液体ヘリウムに浸すことで超伝導状態とし、外部から電気信号を入力。チップを介して出力される信号を調べることで、チップの評価を行える。

エヌエフ回路設計ブロックは、「もともと当社は微小信号の処理が得意なので、それを生かしたソリューション。今回の低雑音システムには、特に、マイクロボルトレベルの電圧を持つ出力信号を、雑音を低く保ったまま100倍、1000倍に増幅する低雑音アンプの技術が貢献している」と説明する。「今回展示したシステムには、外来ノイズをキャンセルする技術と、雑音自体をシステムに入れないようにする技術の両方を用いることで、低雑音を実現した。量子コンピュータ用のチップを開発しても、正しく評価できなくては意味がない。当社のソリューションが、再現性の高い測定や評価に貢献できればと考えている」(同社)

今回展示したシステムは多量子ビット化にも対応可能で、「5〜6Qビット(量子ビット)のチップを評価可能」(同社)とする。さらに、2021年には51Qビットまでのチップを評価できるようシステムの開発を進める。

関連記事

「ISSCC 2021」はオンライン化、日本は論文採択率が高い

「ISSCC 2021」はオンライン化、日本は論文採択率が高い

ISSCC ITPC Far East Regional Subcommitteeは2020年11月17日、オンライン記者説明会を開催し、2021年2月に開催される「ISSCC 2021」の概要と注目論文を紹介した。新型コロナウイルス感染症(COVID-19)の影響で、第68回となるISSCC 2021はオンラインで開催される。 富士通、量子コンピュータ実現に向け研究を本格化

富士通、量子コンピュータ実現に向け研究を本格化

富士通は2020年10月13日、オンラインで研究開発戦略説明会を実施。量子コンピュータの実現に向け、理化学研究所(理研)や東京大学、大阪大学、オランダのデルフト工科大学の4研究機関と共同研究を開始することを明かした。富士通研究所ICTシステム研究所量子コンピューティングプロジェクトのプロジェクトディレクター、佐藤信太郎氏は、「先の長い研究だが、この分野で共同研究先とともに世界をリードし、将来的に社会課題解決に貢献したい」と語った。 ひねくれボッチのエンジニアも感動で震えた「量子コンピュータ至高の技術」

ひねくれボッチのエンジニアも感動で震えた「量子コンピュータ至高の技術」

いよいよ最終回を迎えた「量子コンピュータ」シリーズ。フィナーレを飾るテーマは「量子テレポーテーション」「量子暗号」、そして、ひねくれボッチのエンジニアの私さえも感動で震えた「2次元クラスター状態の量子もつれ」です。量子コンピュータを調べるほどに「この技術の未来は暗いのではないか」と憂うようになっていた私にとって、2次元クラスター状態の量子もつれは、一筋の光明をもたらすものでもありました。 量子もつれ 〜アインシュタインも「不気味」と言い放った怪現象

量子もつれ 〜アインシュタインも「不気味」と言い放った怪現象

今回は、私を発狂寸前にまで追い込んだ、驚愕動転の量子現象「量子もつれ」についてお話したいと思います。かのアインシュタインも「不気味」だと言い放ったという、この量子もつれ。正直言って「気持ち悪い」です。後半は、2ビット量子ゲートの作り方と、CNOTゲートを取り上げ、HゲートとCNOTゲートによる量子もつれの作り方を説明します。 IBM、量子ボリュームで自社最高の「64」を達成

IBM、量子ボリュームで自社最高の「64」を達成

IBMは、量子コンピュータの性能を表す「量子ボリューム」という指標で「64」を達成した。自社製品では最高値となる。 ビットコインの正体 〜電力と計算資源を消費するだけの“旗取りゲーム”

ビットコインの正体 〜電力と計算資源を消費するだけの“旗取りゲーム”

今回から新しいシリーズとして「ブロックチェーン」を取り上げます。さて、このブロックチェーンを理解するために、まずは「ビットコイン」のお話から始めましょう。なぜビットコインか、というのは本文を読んでいただくとして、あらためてビットコインを調べ始めた私がまず発見したものは――「人間を支配するアルゴリズム」でした。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待