EE Times Japan >

LSI >

EUVリソグラフィを補完する自己組織化リソグラフィ:福田昭のデバイス通信(293) Intelが語るオンチップの多層配線技術(14)(2/2 ページ)

» 2020年12月25日 09時30分 公開

[福田昭,EE Times Japan]

配線幅と配線端部のばらつきを減らす

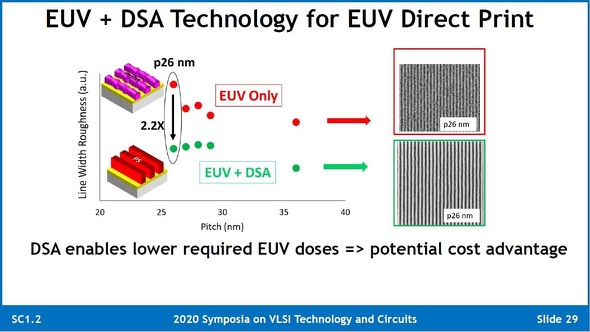

そこでEUVリソグラフィでレジストに平行配線群のパターンを形成したあとで、レジストを配線ではなく、DSAリソグラフィの下地層のパターン形成に使うことを考える。こうすると、例えばピッチが26nmの平行配線パターンを形成したときに、配線幅のばらつき(LWR)が2.2分の1(45%)に減らせるとする。

EUVリソグラフィにDSAリソグラフィを組み合わせることで、配線幅のばらつき(LWR)を45%(2.2分の1)に低減(配線ピッチは26nm)。左は配線ピッチとLWRの関係。右は26nmピッチの平行直線群を形成したパターンの観察像。出典:Intel(クリックで拡大)

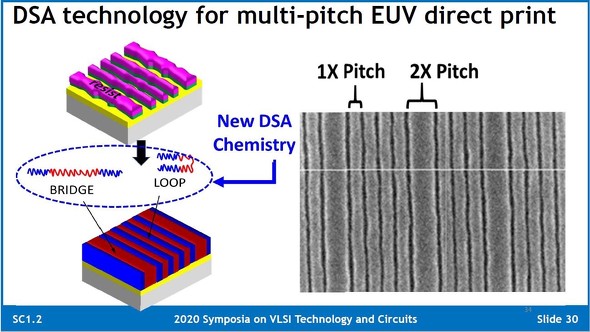

EUVリソグラフィにDSAリソグラフィを組み合わせることで、配線幅のばらつき(LWR)を45%(2.2分の1)に低減(配線ピッチは26nm)。左は配線ピッチとLWRの関係。右は26nmピッチの平行直線群を形成したパターンの観察像。出典:Intel(クリックで拡大)またDSAリソグラフィはEUVリソグラフィと組み合わせることで、基本ピッチ(×1ピッチ)と2倍ピッチ(×2ピッチ)の平行配線パターンを一括して作れるとした。例えばPMMA-b-PS-b-PMMAといった共重合高分子を使う。中央のPS部が長く、両端のPMMA部はPS部の半分と短い。直線状に伸びた共重合高分子は2倍ピッチ、真ん中で折り返した共重合高分子は基本ピッチの要素となる。

基本ピッチ(×1ピッチ)と2倍ピッチ(×2ピッチ)の平行配線パターンをEUVとDSAの組み合わせで形成する。左は原理図。直線状に伸びた共重合高分子は2倍ピッチ、真ん中で折り返した共重合高分子は基本ピッチのパターンとなる。右は試作したパターンの観察像。出典:Intel(クリックで拡大)

基本ピッチ(×1ピッチ)と2倍ピッチ(×2ピッチ)の平行配線パターンをEUVとDSAの組み合わせで形成する。左は原理図。直線状に伸びた共重合高分子は2倍ピッチ、真ん中で折り返した共重合高分子は基本ピッチのパターンとなる。右は試作したパターンの観察像。出典:Intel(クリックで拡大)(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

露光技術の微細化限界を突破する自己組織化技術

露光技術の微細化限界を突破する自己組織化技術

今回から、ArF液浸技術やEUV(極端紫外線)技術などの露光技術の微細化限界を超える、あるいはこれらの露光技術を延命させる次世代のリソグラフィ技術「自己組織化リソグラフィ」をご紹介する。 多層配線の性能を向上させるエアギャップと2次元材料

多層配線の性能を向上させるエアギャップと2次元材料

今回は、多層配線の容量を下げる要素技術「エアギャップ」と、多層配線の抵抗を下げる要素技術「2次元(2D)材料」について解説する。 多層配線のアスペクト比(AR)を高める2つの要素技術

多層配線のアスペクト比(AR)を高める2つの要素技術

配線のアスペクト比(AR)を高める、2つの要素技術について解説する。 多層配線のアスペクト比(AR)と抵抗および容量の関係

多層配線のアスペクト比(AR)と抵抗および容量の関係

今回は、配線のアスペクト比(AR)と配線抵抗および配線容量の関係を概説する。 銅(Cu)配線の微細化と抵抗値の増大

銅(Cu)配線の微細化と抵抗値の増大

引き続き、オンチップの多層配線技術に関するIntelの講演内容を紹介する。今回は、銅配線の寸法と電気抵抗の関係を説明する。 ムーア則の維持に貢献する配線技術

ムーア則の維持に貢献する配線技術

「VLSIシンポジウム」から、オンチップの多層配線技術に関するIntelの講演内容を紹介するシリーズ。将来の配線技術には、サブトラクティブ法や低誘電率絶縁材料などに期待がかかっている。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR