多層配線のアスペクト比(AR)と抵抗および容量の関係:福田昭のデバイス通信(288) Intelが語るオンチップの多層配線技術(9)

今回は、配線のアスペクト比(AR)と配線抵抗および配線容量の関係を概説する。

ARを固定すると抵抗と容量がトレードオフ関係に

半導体のデバイス技術と回路技術に関する国際学会「VLSIシンポジウム」では、「ショートコース(Short Course)」と呼ぶ技術講座を開催してきた。2020年6月に開催されたVLSIシンポジウムのショートコースは、3つの共通テーマによる1日がかりの技術講座が設けられていた。その中で「SC1:Future of Scaling for Logic and Memory(ロジックとメモリのスケーリングの将来)」を共通テーマとする講演、「On-Die Interconnect Challenges and Opportunities for Future Technology Nodes(将来の技術ノードに向けたオンダイ相互接続の課題と機会)」が非常に興味深かった。そこで講演の概要を本コラムの第280回からシリーズでお届けしている。講演者はIntelのMauro J. Kobrinsky氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

本シリーズの第5回からは、多層配線の微細化と性能向上を両立させる要素技術を紹介している。前回は、金属配線の抵抗と容量を大きく左右する、配線の「アスペクト比(AR:Aspect Ratio)」を簡単に解説した。配線の断面における高さ(深さ)と幅の比率がアスペクト比(AR)であること、ダマシン技術による銅配線では、高さ(深さ)の定義にばらつきがあることを説明した。

今回は、配線のアスペクト比(AR)と配線抵抗および配線容量の関係を概説する。始めにアスペクト比(AR)を固定したときの関係、次にARを変化させたときの抵抗と容量との関係を述べる。

ARを高くすると配線の抵抗と容量がともに減少

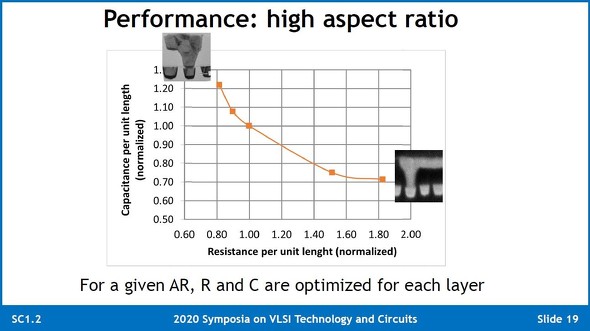

アスペクト比(AR)を固定したときの抵抗(配線長当たり)と容量(配線長当たり)の関係は、それなりに単純だ。抵抗を下げようとすると、あるところから容量が急速に上昇する。逆に容量を下げようとすると、あるところから抵抗が急速に上昇する。すなわち両者にはトレードオフの関係がある。

具体的に数値を挙げて変化を見てみよう。ここでは相対値で考える。例えば抵抗を1.81から1.50に17%下げても、容量は0.71から0.75へと5.6%しか増えない。ところが抵抗を1.00から0.81に19%下げると、容量は1.00から1.21へと21%も増加してしまう。逆の表現をすると、容量を1.21から1.00へ17%下げると、抵抗は0.81から1.00へと23%増える。そして容量を0.75から0.71へと5.3%減らすと、抵抗は1.50から1.81へと21%も増加する。

従ってARが固定された多層配線では、配線層ごとに抵抗と容量の値を最適化する必要がある。

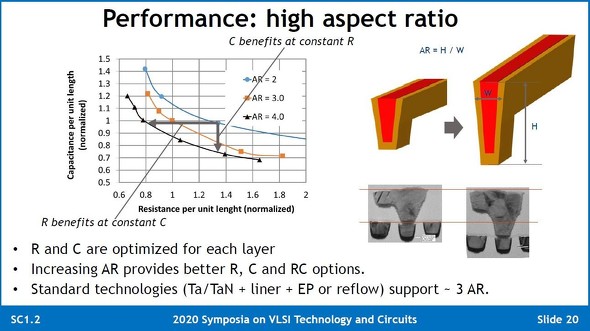

次にARを増やしたり減らしたりすると、抵抗と容量はどのように変化するのだろうか。ARが2(高さが幅の2倍)の配線とARが4(高さが幅の4倍)の配線を比較する。容量を固定すると、ARの増加によって抵抗は減少する。逆に抵抗を固定すると、ARの増加によって容量は減少する。

ARを高めることは、抵抗(R)と容量(C)の積で決まる信号の立ち上がり時間と降下時間を短くすることでもある。回路動作の高速化に寄与する。

だからといってARをいたずらに増やすことは実用的ではない。ダマシン技術のプロセスだと、絶縁膜に細長い溝を切り、その細長い溝に銅金属を埋め込む必要がある。ARを高くすることは、プロセスの難しさが上がることを意味する。標準的なプロセスでは、ARの高さは3前後までとなる。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

銅(Cu)配線の微細化と抵抗値の増大

銅(Cu)配線の微細化と抵抗値の増大

引き続き、オンチップの多層配線技術に関するIntelの講演内容を紹介する。今回は、銅配線の寸法と電気抵抗の関係を説明する。 ムーア則の維持に貢献する配線技術

ムーア則の維持に貢献する配線技術

「VLSIシンポジウム」から、オンチップの多層配線技術に関するIntelの講演内容を紹介するシリーズ。将来の配線技術には、サブトラクティブ法や低誘電率絶縁材料などに期待がかかっている。 オンチップの相互接続技術を過去から将来まで概観

オンチップの相互接続技術を過去から将来まで概観

2020年6月にオンラインで開催された「VLSIシンポジウム」から、オンチップの多層配線技術に関するIntelの講演内容を紹介する。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。 HDD大手Seagateの四半期売上高は前年同期比で2桁の減少

HDD大手Seagateの四半期売上高は前年同期比で2桁の減少

今回は、米Seagate Technologyの2021会計年度第1四半期の業績を紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待