Intelの先端パッケージング技術「EMIB」を支援するEDAツール:DAC 2024で注目(1/2 ページ)

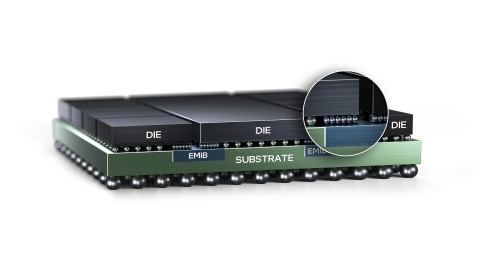

Intelのパッケージング技術「Embedded Multi-Die Interconnect Bridge(EMIB)」は、異種統合マルチチップ/マルチチップレットアーキテクチャの複雑化に対処することを目的とした技術だ。EDAツール大手各社が同技術向けのツールを発表している。

Intelのパッケージング技術「Embedded Multi-Die Interconnect Bridge(EMIB)」は、異種統合マルチチップ/マルチチップレットアーキテクチャの複雑化に対処することを目的とした技術だ。同技術は米国カリフォルニア州サンフランシスコで開催された「DAC(Design Automation Conference)2024」(2024年6月23〜27日)で大きな話題となった。Intelは、2.5D(2.5次元)/3D(3次元) ICなどの幅広い集積技術に対応し、設計から試作、承認までを網羅する先進の統合ICパッケージングソリューションを提供している。

IntelはDACで、大手EDAおよびIPパートナーとの提携を発表し、異種設計ツール/フロー/方法論/再利用可能なIP(Intellectual Property)ブロックがEMIBアセンブリ技術をサポートするために完全に有効かつ適格であることを実証した。

これらの取り組みの中心となるのが、EMIBベースのパッケージ設計をサポートするIntel Foundryの「Package Assembly Design Kit(PADK)」だ。PADKは、チップ設計者がEMIB設計を効率的に完了および検証できるようにする設計ガイド、ルール、スタックアップで構成されていて、チップ設計の複雑さに対処し、EDAツールの有効化促進を目的としている。

PADKは、主要EDAベンダーのツールをサポートするリファレンスフローを実現し、PADK主導のアセンブリ検証を容易にする。以下は、EMIBの有効化に向けたIntel Foundryと主要EDAベンダーとの最近の協業の一例である。

詳細実装の検証が可能、Siemens

Siemens EDAはDAC 2024で、非常に複雑なICや先進パッケージングを設計するためのEMIB有効化のツールの認定を発表した。この認定には、Intel Foundryの「Intel 16」および「Intel 18A」プロセスノード向けのソフトウェア「Solido Simulation Suite」の一部である「Solido SPICE」が含まれる。

Siemens EDAはこれに先立って2024年2月、設計エンジニアが早期パッケージアセンブリの試作や階層型デバイスのフロアプランニング、共同設計の最適化、完全な詳細実装の検証を実施できるEMIBリファレンスフローの提供を発表している。このリファレンスフローは、Intel FoundryのPADKを中心に構築されていて、エンジニアは設計とテープアウトの成功に向けて必要となるあらゆる重要タスクに取り組むことができる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増