AI/HPCの性能を左右する電源供給網の安定化(後編):福田昭のデバイス通信(515) TSMCが解説する最新のパッケージング技術(12)(1/2 ページ)

前編に続き、電源供給網を安定化する技術について解説する。データセンターの電力消費予測と、次世代の電源回路アーキテクチャ、電源供給の効率向上(損失低減)などを取り上げる。

(ご注意)今回は前編の続きです。まず前編を読まれることを強く推奨します。

AIデータセンターの総電力消費は10年で最大3.5倍に急増

前編(前回)では、STCO(システムと製造の協調最適化)で考慮すべき項目「(5)Power delivery efficiency(電源供給の効率)」の概要説明を始めた。具体的には、電源電圧を不安定にする要因、電源インピーダンスの周波数特性、電源インピーダンスの高周波対策をご報告した。

後編ではデータセンターの電力消費予測と、次世代の電源回路アーキテクチャ、電源供給の効率向上(損失低減)などについてご説明する。

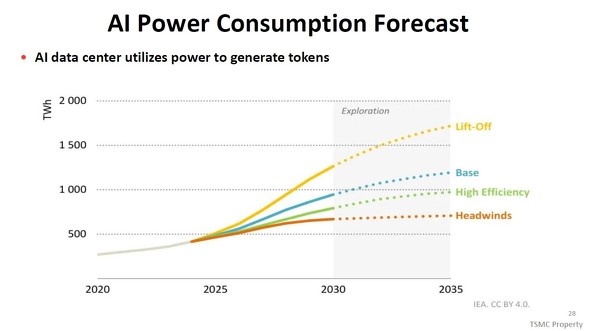

始めはAIデータセンターの総電力消費である。2025年における総電力消費エネルギーは、およそ500TWhとみられる。2030年には700TWh〜1250TWhに拡大すると予測する。そして2035年には750TWh〜1750TWhとさらに上昇する。最悪の場合、10年で3.5倍に増える。

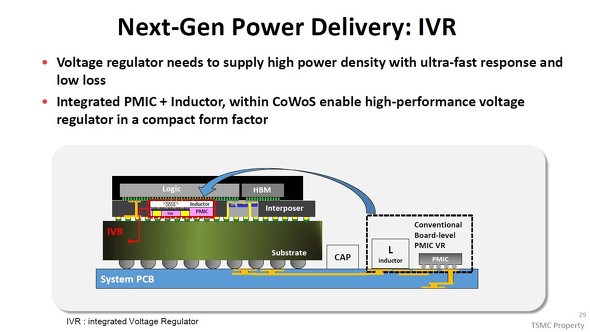

AIデータセンターの総電力消費予測(高め(Lift-Off)から低め(Headwinds)まで、4通りの予測がある)[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

AIデータセンターの総電力消費予測(高め(Lift-Off)から低め(Headwinds)まで、4通りの予測がある)[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)プリント基板の上から先進パッケージの内部に電源回路を移設

総電力消費の上昇を緩和する有力な手段の1つが、電源回路の統合化である。前編でも述べたように、AI/HPC向け高性能プロセッサへの電源電圧は、プリント回路基板に搭載した定電圧回路(VR)や電源管理IC(PMIC)、インダクター(L)などによって供給されてきた。

AI/HPC向け高性能プロセッサを搭載した先進パッケージ(CoWoSなど)が要求する電源の仕様は最近、極めて厳しくなりつつある。供給電力の肥大化(電力密度の増大)、負荷の時間的な変動への反応時間短縮、損失の低減(効率の向上)などだ。

要求に応える手段の1つが、先進パッケージ内部に電源回路を設けることである。具体的には、中間基板(インターポーザ)の内部に電源管理IC(PMIC)とインダクター(L)を埋め込む。「統合化定電圧回路(IVR:Integrated Voltage Regulator)」とも呼ばれる。電源回路の体積が縮小するとともに負荷変動に対する反応速度が高まり、電源回路での損失が減る(電源の効率が上昇する)。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(前編)

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(後編)

- 石炭灰から「レアアース元素」を回収、新日本繊維【訂正あり】

- EVに吹く逆風 デンソーの焦りとロームが求める勝機とは

- 「27年度後半の2nm量産誓う」 Rapidus、解析センター開設

- 経産省、Rapidusに6315億円追加支援 「国益のため必ず成功」

- 半導体産業を下支え 台湾スタートアップの「3つの特徴」とは

- 光電融合チップレットの技術開発を開始 LSTCとimec

- 「技術を束ねて高価値システムに」 デンソーが2030年中計発表

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円