AI/HPCの性能を左右する電源供給網の安定化(後編):福田昭のデバイス通信(515) TSMCが解説する最新のパッケージング技術(12)(2/2 ページ)

IVRの導入で効率が15ポイントから20ポイント向上

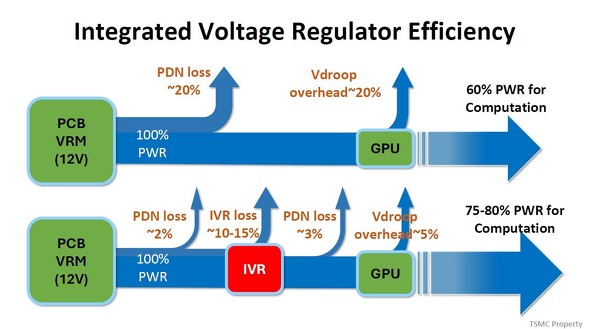

従来の電源供給アーキテクチャ(プリント回路基板の定電圧回路からGPUモジュールに電源を供給する場合)と、新しい電源供給アーキテクチャ(プリント基板の定電圧回路からIVRを経てGPUに電力を供給する場合)で、効率を比較しよう。

従来の電源アーキテクチャでは、定電圧回路モジュール(VRM)の出力電圧12VがGPUモジュールに届くまでに、20%の損失が生じる。GPUモジュールでは12Vを1V前後に降圧するため、さらに20%が失われる。GPUモジュールが受け取る電力は、元の60%に低下する。

新しいアーキテクチャでは、VRMから先進パッケージのIVRまでの距離が短い。損失は2%にとどまる。IVRでは降圧と安定化のために10%〜15%の損失が生じる。そしてIVRからGPUモジュールまでの供給損失が3%、GPUモジュールでの降圧による損失が5%ある。GPUモジュールが受け取る電力は、元の75%〜80%となる。従来のアーキテクチャと比べ、15ポイント〜20ポイントの効率向上が見込める。

電源アーキテクチャと効率(損失)の比較。上は従来のアーキテクチャ。下はIVRを設けた新しいアーキテクチャ[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

電源アーキテクチャと効率(損失)の比較。上は従来のアーキテクチャ。下はIVRを設けた新しいアーキテクチャ[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)10MHz以下の周波数領域で電源インピーダンスが大きく減少

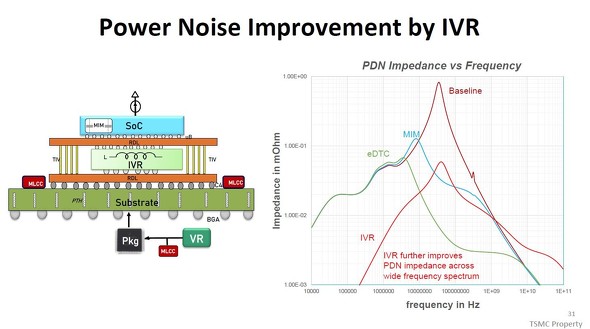

「統合化定電圧回路(IVR:Integrated Voltage Regulator)」による、もう1つの重要なメリットが電源インピーダンスの低減である。前編で述べたMIMキャパシター、eDTCよりも10MHz以下の周波数領域におけるインピーダンスは低い。IVRの電源インピーダンスはピーク周波数がベースラインと同じ数十MHzにあるものの、インピーダンスのピーク値はベースラインと比べて10分の1以下に減っている。

電源インピーダンスの低減は、電源による雑音(電源電圧変動)の低減をもたらす。高周波領域での雑音が減ることにより、高周波領域での信号品質が向上する。

統合化定電圧回路(IVR:Integrated Voltage Regulator)を組み込んだ先進パッケージの電源インピーダンス。左はパッケージの構造。右は電源インピーダンスの周波数特性(縦軸はインピーダンス、横軸は周波数)[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

統合化定電圧回路(IVR:Integrated Voltage Regulator)を組み込んだ先進パッケージの電源インピーダンス。左はパッケージの構造。右は電源インピーダンスの周波数特性(縦軸はインピーダンス、横軸は周波数)[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)(次回に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

関連記事

ネットワークの大規模化と高速化が電気から光への転換を促す

ネットワークの大規模化と高速化が電気から光への転換を促す

「IEDM 2025」におけるTSMCの講演内容を紹介するシリーズ。今回は、「(4)Energy efficient of scale-up networking(ネットワークの大規模化おける消費エネルギー(転送データ当たり)の効率)」を取り上げる。 AI/HPCシステムの死命を制する消費電力・放熱設計(後編)

AI/HPCシステムの死命を制する消費電力・放熱設計(後編)

「IEDM 2025」におけるTSMCの講演内容を紹介するシリーズ。前編に続き、「(3)Thermal dissipation design(消費電力および放熱の設計)」の内容を解説する。 AI/HPCシステムの死命を制する消費電力・放熱設計(前編)

AI/HPCシステムの死命を制する消費電力・放熱設計(前編)

「IEDM 2025」におけるTSMCの講演内容を紹介するシリーズ。「(3)Thermal dissipation design(消費電力および放熱の設計)」を前後編に分けて解説する。 世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに

世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに

米国半導体工業会によると、2026年2月の世界半導体売上高は前年同月比61.8%増の888億米ドルと大幅な増加を記録したという。ただ、地域別では日本のみマイナス成長となっている。日本が前年同月比減となるのは9カ月連続だ。 Micronの四半期業績、利益額と利益率がともに過去最高を更新

Micronの四半期業績、利益額と利益率がともに過去最高を更新

今回は、Micron Technologyの2026会計年度第2四半期(2025年12月〜2026年2月期)の四半期業績を紹介する。 ミニダイ(チップレット)間接続におけるSTCO

ミニダイ(チップレット)間接続におけるSTCO

「IEDM 2025」におけるTSMCの講演内容を紹介する。前回に続き、アウトラインの第3項「System-Technology Co-Optimization (STCO)(システム・製造協調最適化)」の内容を解説する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(前編)

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(後編)

- 石炭灰から「レアアース元素」を回収、新日本繊維【訂正あり】

- EVに吹く逆風 デンソーの焦りとロームが求める勝機とは

- 「27年度後半の2nm量産誓う」 Rapidus、解析センター開設

- 経産省、Rapidusに6315億円追加支援 「国益のため必ず成功」

- 半導体産業を下支え 台湾スタートアップの「3つの特徴」とは

- 光電融合チップレットの技術開発を開始 LSTCとimec

- 「技術を束ねて高価値システムに」 デンソーが2030年中計発表

- Rapidus、IIM-1を「世界初の前/後工程一貫工場に」