強誘電体NANDの電源を大幅に下げる、次世代SSDの可能性を開く新技術:メモリ/ストレージ技術 SSD(2/2 ページ)

» 2010年06月09日 00時00分 公開

[前川慎光,EE Times Japan]

コラム:誤り訂正強度を状況に合わせる手法提案

東京大学大学の竹内健氏の研究グループがIMW 2010で発表したメモリコントローラについてのタイトルは、「Post-manufacturing,17-times acceptable Raw Bit Error Rate Enhancement, Dynamic Codeword Transition ECC Scheme for Highly Reliable Solid-State Drives, SSDs」である。

この発表の基本アイデアは、NAND型フラッシュメモリの状況に合わせて、ECC(Error Correcting Code:誤り訂正符号)による誤り訂正機能の強度を変えようというものだ。すなわち、NAND型フラッシュメモリを使い始めた当初の誤り率が低いとき(期間)には、ECC処理の強度を低くし、長期間使用するなどして誤り率が高まったときには、ECC処理の強度を高くする。

具体的には、NAND型フラッシュメモリの書き換え回数やエラー回数といった指標を監視し、あらかじめ決めておいたしきい値を上回ったときにECCのコード長(codeword)を変える。

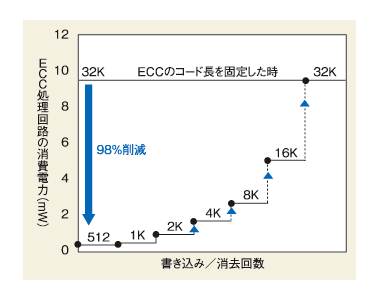

図A ECC(誤り訂正符号)のコード長を変える手法を提案 NAND型フラッシュメモリの書き換え/消去回数に応じて、例えば、512バイトから32Kバイトまで段階的にECCのコード長を変える。そうすれば、NAND 型フラッシュメモリの誤り率が低い期間の消費電力や処理時間を減らせる。出典:東京大学竹内研究室

図A ECC(誤り訂正符号)のコード長を変える手法を提案 NAND型フラッシュメモリの書き換え/消去回数に応じて、例えば、512バイトから32Kバイトまで段階的にECCのコード長を変える。そうすれば、NAND 型フラッシュメモリの誤り率が低い期間の消費電力や処理時間を減らせる。出典:東京大学竹内研究室このような仕組みをコントローラに実装すれば、特にNAND 型フラッシュメモリの誤り率が低い期間における、ECC処理ブロックでの消費電力や処理時間の低減が見込める(図A)。ECC処理が強力だと、許容できる誤りビットは増えるものの、消費電力や処理時間が増大してしまうからだ。信号処理技術に強みを持つベンチャー企業「シグリード」と共同で発表した。「この技術は、すぐにでも実装可能だ」(竹内氏)という。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR