強誘電体NANDの電源を大幅に下げる、次世代SSDの可能性を開く新技術:メモリ/ストレージ技術 SSD(1/2 ページ)

SSDの弱み、「アキレス腱」は何か。それは、SSD内部に使うNAND型フラッシュメモリの消費電力をなかなか下げられていないことのようだ。

SSDの弱み、「アキレス腱」は何か。それは、SSD内部に使うNAND型フラッシュメモリの消費電力をなかなか下げられていないことのようだ。

SSDに使われているインターフェイス技術の進展はいちじるしく、次々と新技術が提案されている。サーバーや組み込み機器の用途では、インターフェイスを高速化する要求は高いからだ。ところが、SSDのインターフェイスが高速になればなるほど、SSDの内部で動くNAND型フラッシュメモリの書き込み/読み出し速度との隔たりが生まれる。NAND型フラッシュメモリの書き込み/読み出し速度は、インターフェイスの速度に比べると大幅に遅い*1)。

処理速度を上げるには、複数のNAND型フラッシュメモリを並列に処理させればよい。しかし、複数のNAND 型フラッシュメモリを同時に動かすとその分、消費電力が大きくなってしまう。SSDの処理性能を高めるためとはいえ、消費電力が大きく増えてしまうことは許されない。つまり、NAND型フラッシュメモリの消費電力がSSDの処理性能を高める足かせとなってしまっているのである。

東京大学大学院工学系研究科電気系工学専攻の准教授である竹内健氏は、「今後、低消費電力化を鍵にした研究開発を、真剣に進める必要がある」と指摘する。

全方位からの取り組みが重要

NAND型フラッシュメモリの消費電力を下げるには、メモリ全体を幾つかの要素に分けて考える必要がある。これは主に4つの要素に分けられる。(1)メモリセルに印加する電圧を生成するブロック、(2)メモリチップ間を接続するインターフェイス、(3)メモリコア、(4)メモリセルの4つ。このほか、NAND型フラッシュメモリの頭脳とも言うべきコントローラー(制御ブロック)も重要である。

竹内氏の研究グループはすでに、(1)の電力生成ブロックについての研究を進めており、2009 年の「ISSCC(IEEE InternationalSolid-State Circuits Conference)」で、研究の進展を発表した。

さらに、(4)のメモリセルと、NAND型フラッシュメモリのコントローラについても、消費電力削減を目指した研究開発も進めており、2010年5月に最新成果を公開した。いずれも、2010年5月16 〜 19日に韓国ソウル市で開催された「IEEE 2nd International Memory Workshop(IMW 2010)」で発表したもの。本稿ではIMW 2010で特に注目を集めたという(4)のメモリセルの低消費電力化に向けた新技術を紹介する。

ディスターブ耐性を維持し電源電圧を下げる

発表のタイトルは、「A 1.0V Power Supply,9.5GByte/sec Write Speed, Single-Cell Self-Boost Program Scheme for Ferroelectric NAND Flash SSD」。強誘電体材料を使ったNAND型フラッシュメモリ(強誘電体NANDメモリ)の電源電圧を1Vに下げられることを示した発表である。

強誘電体NANDメモリとは、NAND 型フラッシュメモリのゲート絶縁膜に強誘電体を使ったもの。これまでは、電源電圧を1Vにまで下げると、ディスターブ(誤った書き換え)に対する耐性が劣化してしまうという課題があった。非書き込みセル(ディスターブセル)にデータを誤書き込みしないためには、3V程度のビットライン電圧(電源電圧)が必要だった。

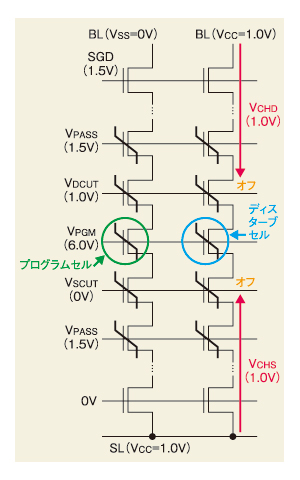

図1 「SCSB(Single-Cell Self-Boos)」と呼ぶ手法を提案 ディスターブ耐性をそのままに電源電圧を下げることを目的に、データ書き込みの新しい手法を考案した。ディスターブセルへの誤書き込みを防ぐための、隣接するセルをオフにする処理や手順が新しい。出典:東京大学竹内研究室

図1 「SCSB(Single-Cell Self-Boos)」と呼ぶ手法を提案 ディスターブ耐性をそのままに電源電圧を下げることを目的に、データ書き込みの新しい手法を考案した。ディスターブセルへの誤書き込みを防ぐための、隣接するセルをオフにする処理や手順が新しい。出典:東京大学竹内研究室そこで今回、ディスターブ耐性をそのままに電源電圧を下げるべく、「SCSB(Single-Cell Self-Boost)」と呼ぶ方式を新たに提案した。強誘電体NANDメモリならではの技術で、データを書き込む前段階に、非書き込みセルにつながったビットライン電圧を1Vに設定し、非書き込みセルの両隣のメモリセル(トランジスタ)をオフにするというもの(図1)。このような前処理をすることで、データ書き込み時に、オフになった2つのメモリセルに囲まれた非書き込みセルの電位が高まり、誤書き込みが防げるとする。「電源電圧を1Vに下げたことで、電源電圧1.8VのNAND型フラッシュメモリに比べ、消費電力を86%削減できる」(竹内氏)。

電源電圧には最適値があり、1V程度が適しているとする。1Vより下げると、書き込み電圧/消去電圧を生成するチャージポンプ回路の段数が増え、結果として全体の消費電力が上昇してしまうからだ。

なお強誘電体NANDメモリは、書き込み電圧/消去電圧が+6V/−6Vと低いという特徴がある。一般的な浮遊ゲート構造のNAND型フラッシュメモリの場合は20V程度である。書き込み電圧/消去電圧が低い分、チャージポンプ回路の段数を減らせるため、低消費電力化の観点でもともと優位だった。

今回の成果は、産業技術総合研究所の酒井滋樹氏の研究グループと共同で進めてきた強誘電体NANDメモリの実用化に向けた取り組みを、一歩前に進めたもの。「強誘電体NANDメモリの新たな可能性を示した成果だ」(同氏)。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増