EE Times Japan >

プロセス技術 >

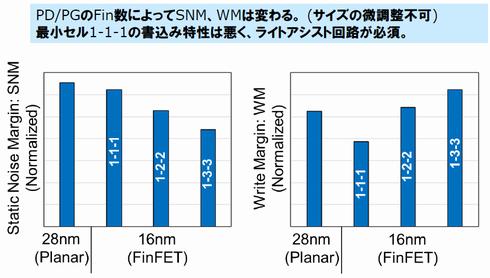

「経験で設計すると失敗する」、ルネサスが提示する16nm FinFET SRAMの課題:メモリ/ストレージ技術(2/3 ページ)

» 2015年02月17日 08時30分 公開

[村尾麻悠子,EE Times Japan]

アシスト回路を開発

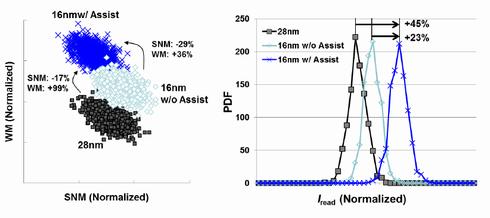

ただし、FinFETの導入と、プロセスの微細化によって新たな課題も出ている。それがデバイス素子のばらつきだ。ばらつきが増大することで、デバイスの下限動作電圧特性が悪化する傾向があり、その対策として回路的に工夫する回路技術(以下、アシスト回路)が導入されている。従来は、読み出し動作時の安定動作を確保するため、アクセス時にワード線の電圧をわずかに下げる工夫をしていた。しかし、この方式では、書き込み時の動作マージンの悪化や、読み出し速度が著しく低下するなどの課題があった。

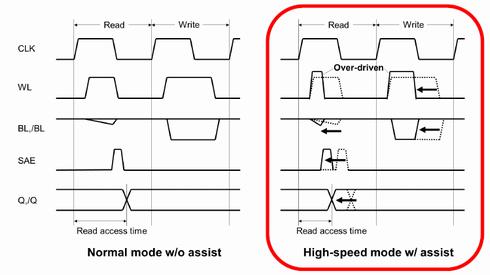

これに対し、ルネサスは、FinFETの特徴を生かし、これまでとは逆にワード線電圧をわずかに昇圧(オーバードライブ)し、読み出し時と書き込み時でそのパルス幅を変えるというアシスト回路方式を採用。これにより、読み出し時と書き込み時の動作マージンを確保しつつ、高速な読み出し動作を実現した。

新アシスト回路の概要。左が従来の技術で、右の赤枠内が新しいアシスト回路技術。ワード線の電圧を少しオーバードライブさせることで、読み出しの速度が向上する(クリックで拡大) 出典:ルネサス エレクトロニクス

新アシスト回路の概要。左が従来の技術で、右の赤枠内が新しいアシスト回路技術。ワード線の電圧を少しオーバードライブさせることで、読み出しの速度が向上する(クリックで拡大) 出典:ルネサス エレクトロニクス今回のアシスト回路技術は、オーバードライブして、かつ短いパルスにした点が鍵だという。「プレーナ型MOSFETでは、ワード線の電圧を上げると読み出し性能は悪くなる。だが、FinFETではPMOSが強くなり読み出し側に十分なマージンができる。そのため、ワード線の電圧を上げられる」(新居氏)。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- Musk氏は「半導体製造の再定義」を目指すのか

- 世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- 300mmファブ装置の投資額、2年連続で2桁成長へ

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- Intelがアイルランド工場を完全子会社化、Apolloから49%買い戻し

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

Special SitePR

あなたにおすすめの記事PR