「経験で設計すると失敗する」、ルネサスが提示する16nm FinFET SRAMの課題:メモリ/ストレージ技術(1/3 ページ)

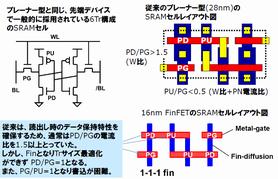

ルネサス エレクトロニクスは、16nm FinFETプロセスを用いてSRAMを試作したと発表した。プレーナ型MOSFETを使う場合に比べて低い動作電圧で高速読み出しに成功しているが、一方でFinFETと、微細化プロセスを用いたことによる課題も増えている。

セミコンダクタポータルが主催した「SPIフォーラム」(2015年1月30日、東京都内)では、ルネサス エレクトロニクス 第一ソリューション事業本部 コア技術事業統括部 設計基盤ライセンス推進部 部長の新居浩二氏が登壇し、TSMCの16nm FinFETプロセスで試作したSRAMについて語った。

同SRAMは、16nmプロセス以降の車載情報機器用SoC(System on Chip)向けの回路技術を用いて作成されたもの(関連記事:ルネサス、16nm FinFETを用いたSRAMを開発)。標準的な電源電圧よりも20%低い0.7Vで、641ps(ピコ秒)の高速読み出しを実現し、動作電力を約40%削減したという。ルネサスは、この開発結果を、「IEDM(International Electron Devices Meeting) 2014」(2014年12月15〜17日、米国カリフォルニア州)でも発表している。

高性能なマイコンに不可欠なSRAM

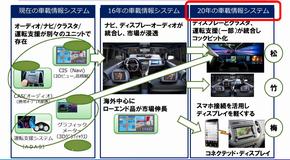

ルネサスにとって、車載は最も注力する分野の1つである。主なターゲットは、車載インフォテインメントシステムだ。2020年には、カーオーディオやカーナビゲーションシステム、ADAS(運転支援システム)などを全て統合した「統合コックピット」の実現を目指している。統合コックピットは、2014年9月に開催したプライベート展「Renesas DevCon Japan 2014」で初めて披露した。

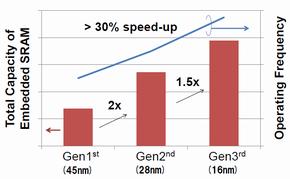

統合コックピットのような車載インフォテインメントシステムでは、非常に高性能なリアルタイム処理が要求される。こうした処理が可能なマイコンを実現するには、高性能なSRAMが欠かせないと、新居氏は話す。そのため、消費電力を抑えつつ高性能化を図れるFinFETは、SRAMにとっても魅力的だという。ルネサスの車載情報機器向けSoC「R-Car」シリーズでは、世代が進むごとにSRAMの搭載容量が増加している。量産体制に入ろうとしている第2世代(Gen 2)R-CarのSRAMの容量は100Mビットを超え、開発中の第3世代(Gen 3)では1.5Gビット以上を狙う。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増