EE Times Japan >

プロセス技術 >

「経験で設計すると失敗する」、ルネサスが提示する16nm FinFET SRAMの課題:メモリ/ストレージ技術(3/3 ページ)

» 2015年02月17日 08時30分 公開

[村尾麻悠子,EE Times Japan]

“経験で設計”すると失敗する

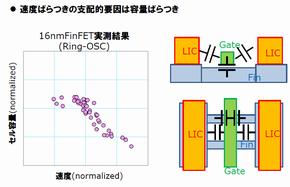

新居氏は、FinFET SRAMの懸念事項として、特性のばらつきの大きさを挙げている。同氏は「ウエハー間、ロット間、同じウエハー内のダイのばらつきなど、グローバルな(包括的な)ばらつきがやはり大きく、ここが最も気にしているところだ」と述べる。さらに「Finになって、いろいろな所に寄生容量が増えた。そのため、“本当に消費電力が下がるのか”という点についてはわれわれも心配している」(同氏)と懸念を口にする。こうしたFinに起因する容量のばらつきは28nmプロセスのプレーナ型MOSFETに比べて増大し、これが速度ばらつきにもつながっているという。

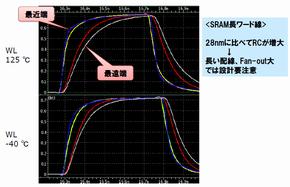

さらに、「配線抵抗が思ったよりも大きい」(新居氏)ことも課題だ。28nmに比べてR(抵抗)C(容量)が増大するので、速度が出ない、動作マージンが取れないといった問題につながると指摘している。同氏は、「今までの経験で設計すると失敗するおそれがある。きちんとRとCを計算して設計しなければならない」と続けた。

関連記事

ルネサス、16nm FinFETを用いたSRAMを開発

ルネサス、16nm FinFETを用いたSRAMを開発

ルネサス エレクトロニクスは2014年12月、16nmプロセス世代以降の車載情報機器用SoC(System on Chip)向け回路技術を開発したと発表した。 TSMC、16nm FinFETのリスク生産を開始

TSMC、16nm FinFETのリスク生産を開始

TSMCが16nmプロセスを適用したFinFETのリスク生産を開始した。開発スケジュールは予定よりも早く進んでいるようだ。今後は、AppleやQualcommなどが、新しい世代のFinFETの製造を、TSMCとSamsung Electronicsのどちらにどの程度発注していくのかが注目される。 Samsungが14nm世代のFinFETを展示、仕様は明かさず

Samsungが14nm世代のFinFETを展示、仕様は明かさず

Samsung Electronics(サムスン電子)が、ARM主催のイベントで14nm世代のFinFETプロセス技術を適用したチップを発表した。TSMCもその直前に16nm FinFETプロセスを用いたARM「Cortex-A57」の検証を行っているが、ある専門家は、16/14nm FinFETの性能については、SamsungとTSMCは互角だとみている。 動作電圧0.4V以下を実現する技術を開発、スマホの消費電力も1/10になる!?

動作電圧0.4V以下を実現する技術を開発、スマホの消費電力も1/10になる!?

新エネルギー・産業技術総合開発機構(NEDO)と超低電圧デバイス技術研究組合(LEAP)は、動作電圧が0.4V以下のロジックLSIやメモリを実現できる技術を開発した。これらの技術を使ったLSIを搭載した機器は、消費電力を1/10に低減できる可能性がある。 「SSDが壊れる」まで(前編)

「SSDが壊れる」まで(前編)

ノートPCなどのストレージとして急速に市場が拡大しているSSD(Solid State Drive)。その信頼性に対するイメージはHDDと比較されることが多いが、「平均故障間隔」と「年間故障率」の数値を単純に比較すればいいというわけではない。そこで今回は、SSDの寿命にかかわる要素を解説する。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- Musk氏は「半導体製造の再定義」を目指すのか

- 世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- 300mmファブ装置の投資額、2年連続で2桁成長へ

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- ヒューマノイドはどこまで現実になっているのか

- Intelがアイルランド工場を完全子会社化、Apolloから49%買い戻し

Special SitePR

あなたにおすすめの記事PR