ARMから見た7nm CMOS時代のCPU設計(1):福田昭のデバイス通信(12)(1/2 ページ)

ARMにとって「IEDM」は非常に重要だ。この会議で議論されるトランジスタ技術が同社のCPUアーキテクチャの行方を左右するからである。ARMは「IEDM 2014」で、CPU設計とデバイス・プロセス技術の関わりを解説する講義を行った。今回から、その内容を複数回にわたってお届けする。

CPU設計企業がデバイス技術に積極的にコミット

半導体のデバイス技術とプロセス技術に関する国際会議「IEDM(International Electron Devices Meeting)」では、カンファレンスの前日に「ショートコース(Short Course)」と呼ぶ1日間のセミナーを開催している。「IEDM 2014」(2014年12月15〜17日、米国サンフランシスコ)では、「7nm CMOS技術の課題(Challenges of 7nm CMOS Technologies)」と題したショートコースが開催され、1日間で5つの講義が実施された。

5つの講義の中で最も興味深かったのは、英国ARM社の設計者による、回路設計に関する解説だった。「Circuit Application Requirements(回路に応用するための要望)」、またのタイトルを「CPU Design and IEDM(CPU設計とIEDM)」とわざと付けてくれたこの講演は、CPU設計とデバイス・プロセス技術がどのように関わっているかを、積極的に分かりやすく説明するものだった。

講演タイトルのスライド。講演者のGreg Yeric氏は、ARM社のシニアプリンシパル・デザイン・エンジニア。設計と製造の最適化、将来デバイスのモデリングなどを担当している(講演当時の資料から) 出典:ARM

講演タイトルのスライド。講演者のGreg Yeric氏は、ARM社のシニアプリンシパル・デザイン・エンジニア。設計と製造の最適化、将来デバイスのモデリングなどを担当している(講演当時の資料から) 出典:ARM またのタイトル「CPU設計とIEDM」とともに講演の概要を示したスライド。CPU設計の概要、なぜIEDMと関わるのか、設計者にとって最も有り難いIEDM論文の書き方、将来に向けてのアイデア、といった項目が並んでいる 出典:ARM

またのタイトル「CPU設計とIEDM」とともに講演の概要を示したスライド。CPU設計の概要、なぜIEDMと関わるのか、設計者にとって最も有り難いIEDM論文の書き方、将来に向けてのアイデア、といった項目が並んでいる 出典:ARM設計技術者とデバイス技術者の短くない距離

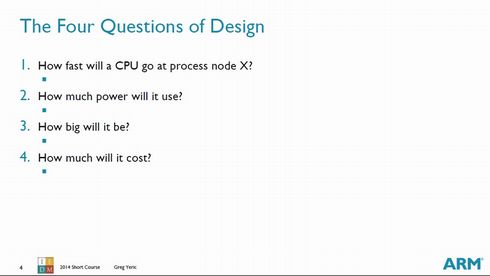

CPUの設計者がデバイス技術者にする質問は、常に同じだという。それは、(1)設計ノードの進化によってCPUはどのくらい速くなるのか、(2)消費電力はどのくらいか、(3)シリコンダイはどのくらいの大きさになるのか、(4)コストはどのくらいか、といったものである。CPUを載せるシステムによって与えられる条件は違ってくるものの、質問の基本は変わらない。

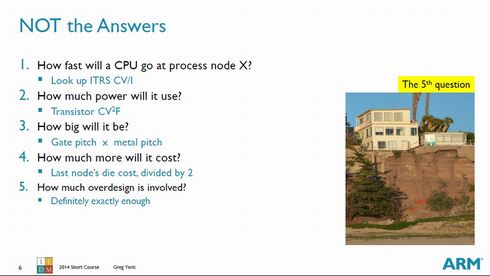

これらの質問に対するデバイス側の回答は下記のようなものだという。(1)ITRSロードマップのCV/Iを読め、(2)トランジスタの電力消費はCV2F(容量×電圧の2乗×動作周波数)だ、(3)ゲートピッチとメタルピッチの積で決まる、(4)前世代の設計ノードに比べて半分になる、である。しかし残念なことに、これらの回答はCPU設計者にとっては回答の意味を成していない。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- メモリも中国が猛追 YMTCは新工場建設

- 560億ドル投資でも「需要に追い付けない」 AI急成長でTSMC表明

- 「AI特需」の恩恵届かぬ日本企業 Gartnerが見る2026年半導体市場

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- SAIMEMORYの垂直ビルド構造メモリ開発がNEDO採択

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- 「Rapidusの隣」に光電融合パッケージ開発拠点、28年度の完成目指す