デジタル化の中で浮沈を決めた“半導体設計の本質”:この10年で起こったこと、次の10年で起こること(3)(2/3 ページ)

半導体にもデジタル化の波

先に述べた3つのデジタル化の利点の3番目、「いつでもどこでも」が「誰でも」に広がった。デジタル回路は機能記述と呼ばれる言語でできている。この機能記述がデジタル化によって商品として扱われるようになった。IPと呼ばれる完成した機能(=ARMのCPUやImagination TechnologiesのGPUなど)を買ってくる。これを半導体工場で作れるように組み込んでいくだけでよい。しかし、これだけでは誰が作っても同じデジタルチップになってしまう。

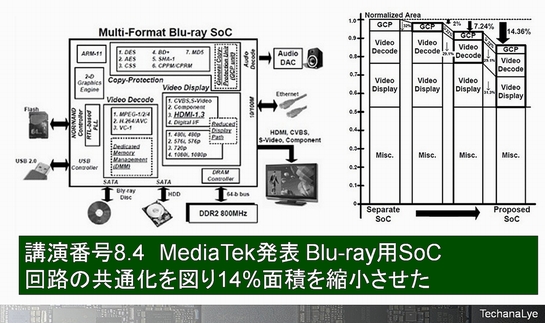

図1は半導体業界で最も権威のある学会「国際固体素子回路会議」(ISSCC)の2009年開催(ISSCC 2009)で発表された台湾MediaTekの論文資料の一部である。デジタルチップの雄としてDVDやBlu-rayで市場を席巻し、中国の山寨(さんさい)機などでも巨大な市場を形成したMediaTekは、単にデジタル化を行って市場を奪ったわけではない。重複する機能や能力を共通化するなどデジタルの中身を最適化して、面積を絞り込んでいることを報告している。

たくさんの機能を搭載するSoC(System on Chip)の場合、買ってきたり、自前で設計したりした既存/新規のIP(機能)をそのまま使い、バスでつなぐのが通例である。しかしMediaTekは異なる機能の内部まで精査し、重複する機能を共通化させることで、大幅な面積(≒コスト)削減を果たしている。この発表はMediaTekの強さの神髄をのぞかせるものであった。

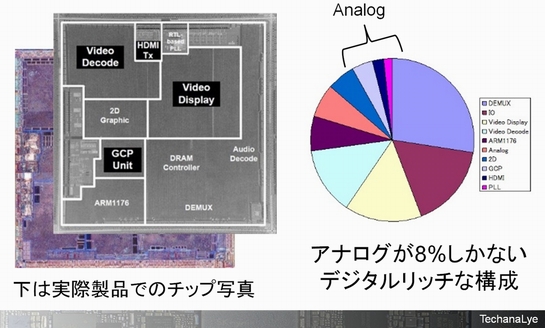

図2は同じくISSCC2009で発表され、2010年から数年間、世界中の多くの製品に活用されたMediaTekのBlu-rayチップである。ISSCCの発表に使われたチップ図と実際に発売されたチップは同じものであった。内部のほとんどがデジタル化されており、一部インタフェース(アナログ端子対応)のみがアナログ回路として搭載されている。アナログ比率はチップの実に8%という小ささである。アナログ回路を最小化するということは、製造ばらつきなどプロセス起因の問題を最小化するということにもつながっている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増