MIPI D-PHYブリッジIC、ラティスが製品化:FPGAとASSPのいいとこ取り(1/2 ページ)

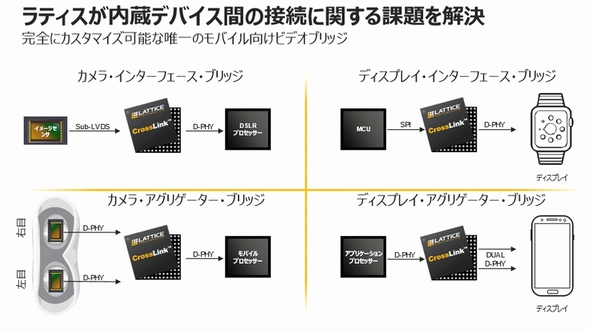

ラティスセミコンダクターは、モバイル機器に搭載されたカメラや表示装置で用いられる主要なプロトコルに対応したMIPI D-PHYブリッジIC「CrossLink」を発表した。

ラティスセミコンダクターは2016年5月30日、モバイル機器に搭載されたカメラや表示装置で用いられる主要なプロトコルに対応したMIPI D-PHYブリッジIC「CrossLink」を発表した。このICはFPGAとASSPの特長を併せ持つ「プログラマブルASSP(pASSP)」と位置付けており、「まったく新しいカテゴリーの製品」という。

モバイル機器に搭載されるアプリケーションプロセッサと、イメージセンサーやディスプレイパネル間でデータ転送行うために、MIPI規格のインタフェースが広く採用されている。しかし、Sub-LVDSやSPI(Serial Peripheral Interface)など、互換性のないインタフェースに対応したデバイスも少なくない。また、入力数や出力数で複数チャネル必要となるシステムもある。

競合と比較して消費電力を25〜50%削減

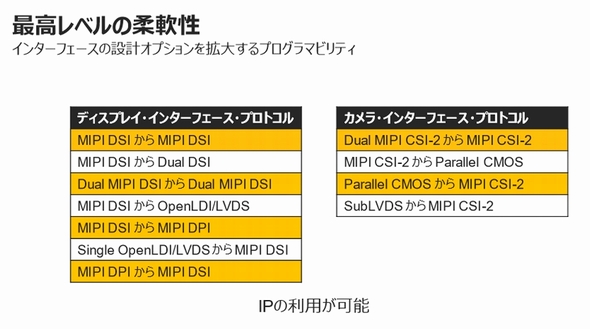

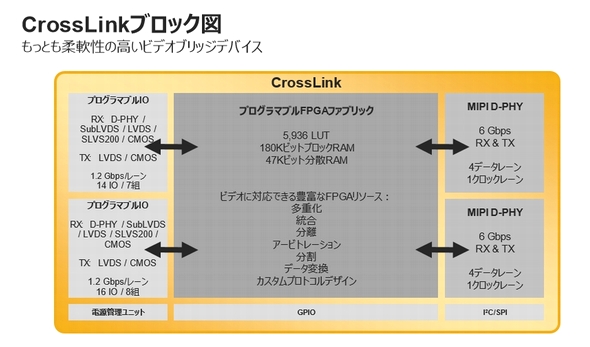

これらのニーズに対応したのがCrossLink。12Gビット/秒の帯域幅で、解像度は最大4k UHD(Ultra High Definition)に対応するMIPI D-PHYブリッジデバイスである。MIPI D-PHYの他、MIPI CSI-2、MIPI DSI、MIPI DPIを始め、CMOS、Sib-LVDS、LVDSなどのインタフェースをサポートしている。

CrossLinkは、最大2個のMIPI D-PHYブロックをハードIPコアで内蔵している。各ブロックは最大4個のデータレーン及び1個のクロックを備え、送受信をサポートする。FPGAファブリックには、カスタマイズ用に5936個のLUT(ルックアップテーブル)、容量180kビットのブロックRAM、47kビットの分散RAMなどを搭載している。

データレート幅は、内蔵した2個のハードD-PHYを利用すると、レーン当たり最大1.5Gビット/秒、プログラマブル差動I/Oを利用すると最大1.2Gビット/秒となる。この他、最大30本(15対)のプログラマブル差動I/Oや、最大10本の汎用I/O、10kHz及び48MHzの発振器、PLLさらには電源管理ユニットなども集積した。

小型パッケージの採用や消費電力の節減も特長の1つである。36端子のWLCSPは、外形寸法が2.46×2.46mmで、専有面積は6mm2である。競合製品に比べると1/2〜1/3のスペースで済むという。産業機器用途向けの80端子CTFBGAも含め、用途に合わせ4種類のパッケージを用意している。消費電力は、アクティブ状態で100mW。競合製品に比べて25〜50%削減しているという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

CrossLinkのパッケージ外観 出典:ラティスセミコンダクター

CrossLinkのパッケージ外観 出典:ラティスセミコンダクター