スピン注入型MRAMの微細化(スケーリング):福田昭のストレージ通信(33) 次世代メモリ、STT-MRAMの基礎(11)(2/2 ページ)

垂直磁気記録方式STT-MRAMの微細化(試作結果)

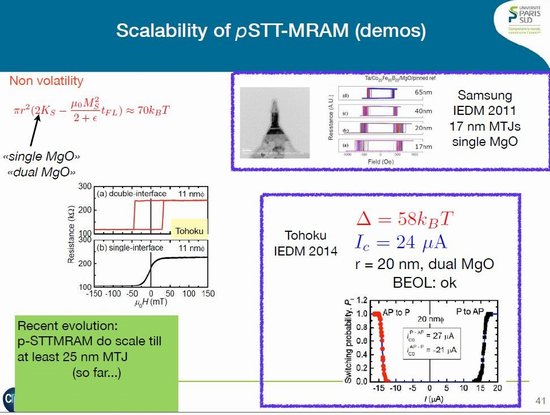

実際にp-STT MRAMをかなり微細な加工寸法で試作した事例を、幾つか紹介する。東北大学の研究チームは、二重トンネル障壁層を備えた垂直磁気記録のMTJ素子を試作し、直径20nmの素子で磁化反転を確認した。磁気異方性エネルギーがボルツマン定数と絶対温度の積の58倍、スイッチング電流が24μAという特性を得ている。2014年に国際学会IEDMで発表した。

韓国のSamsung Electronicsは、直径が17nmと小さな垂直磁気記録MTJ素子で、磁界によって抵抗値を変化できることを確認した。2011年に国際学会IEDMで発表した。また東北大学は、直径が11nmと微小な垂直磁気記録MTJ素子を試作し、二重トンネル障壁を備えたタイプで磁界による抵抗変化を確認している。

これらの試作結果から、p-STT MRAMは少なくとも25nmまでは微細化できるとした。

MRAMによるDRAMの置き換えは難しい

講演者のDevolder氏は、MRAMの将来についてもコメントした。

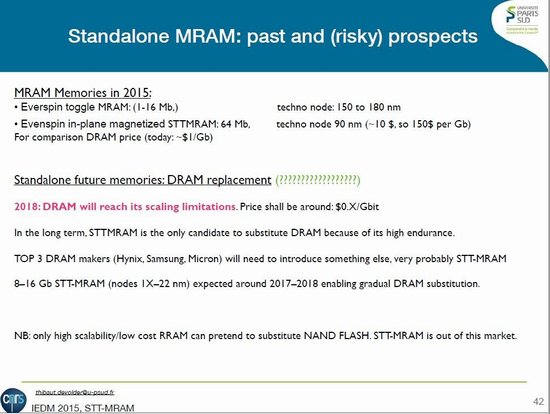

現在のところ、MRAMの製品を量産出荷している企業は技術ベンチャーのEverspin Technologiesだけである。同社は初めてのスピン注入型MRAM(面内磁気記録方式)を製品化し、量産中だ。記憶容量は64Mbitと小さく、微細加工技術は90nmとそれほど厳しくない。価格は、10ドル前後とみられる。記憶容量当たりの単価に換算すると150米ドル/Gbitとなり、DRAMの約1米ドル/Gbitに比べると桁違いに高い。

単価と記憶容量にこれだけの巨大な開きがあると、MRAMがDRAMを置き換えるというシナリオには数多くの疑問符が付いてしまう。

ただし、MRAMには書き換え回数に制限がないという重要な特長がある。競争相手として取り上げられる次世代メモリのPCM(相変化メモリ)とReRAM(抵抗変化メモリ)では、達成がほぼ不可能な特性だ。従ってDRAM(あるいはSRAM)を置き換えられる可能性を備えた次世代メモリはMRAMだけになる。

希望的観測としては、2017年〜2018年ころに10nm〜20nmの微細加工によって8Gbit〜16Gbitの大容量STT-MRAMを実現できれば、DRAMを代替する可能性が出てくる。

(次回に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

関連記事

微細化、「3nmまでいくのでは」

微細化、「3nmまでいくのでは」

「ムーアの法則」の生みの親であるGordon Moore氏が、ハワイの自宅でベルギーIMECのビデオインタビューに応じ、未来の技術に関する自身の見解や、1965年以来半導体業界に大きな影響を及ぼし続けてきたムーアの法則の今後について語った。87歳となった同氏は、謙虚なエンジニアはいつまでも自分を笑いの種として語れることを示してみせた。 10nmプロセス以降に焦点、“微細化のその先”も

10nmプロセス以降に焦点、“微細化のその先”も

2016年6月に米国ハワイで開催される「2016 VLSI Symposia on VLSI Technology and Circuits」では、10nm以降のプロセス技術の研究成果も多数発表される予定だが、“微細化のその先”についても、これまで以上に活発な議論が行われるようだ。 0.03μm2のSRAMから最先端のIII-V族FinFETまで

0.03μm2のSRAMから最先端のIII-V族FinFETまで

米国ハワイで2016年6月13〜16日に開催される「VLSI Symposia on VLSI Technology and Circuits(以下、VLSIシンポジウム)」は、最先端の半導体デバイス/回路技術が一堂に会する国際会議だ。VLSIシンポジウムを実行するVLSIシンポジウム委員会は4月20日、都内で記者説明会を開催し、同イベントの概要と注目論文を紹介した。 樹脂に部品埋め込み→印刷で完成する電子回路

樹脂に部品埋め込み→印刷で完成する電子回路

オムロンは2016年6月2日、樹脂に電子部品や半導体デバイスを埋め込み固定し、その上からインクジェット印刷でパターンを印刷し、電子回路を形成する技術を発表した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待