SanDiskが語る、抵抗変化メモリのセルアレイとセルの選択:福田昭のストレージ通信(52) 抵抗変化メモリの開発動向(11)(2/2 ページ)

セル選択素子(セレクタ)の理想と現実

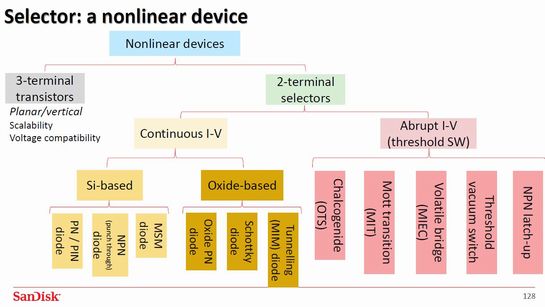

セル選択素子(セレクタ)には大別すると、3端子素子と2端子素子がある。3端子素子とはトランジスタのことだ。横方向(シリコン表面と平行な方向)にレイアウトするMOSFETと、縦方向(シリコン表面と垂直な方向)にレイアウトするバイポーラ・トランジスタがある。消費電流を下げるという観点からはMOSFETが望ましい。メモリセルのシリコン面積を縮小する(製造コストを下げる)という観点からは、バイポーラ・トランジスタが都合が良い。

ただしいずれにしても、1個のトランジスタと1個の記憶素子で1個のメモリセルを構成するというアーキテクチャでは、DRAMよりも低い製造コストの実現が困難である。安定かつ消費電力の低い動作を優先し、DRAMよりも高い製造コストを許容する場合は、MOSFETをセレクタに採用することが最善策だろう。

しかしDRAMよりも低い製造コストを目指すとなれば、話は別である。2端子素子のセレクタ技術を開発し、記憶素子(抵抗変化素子)とセレクタを重ねる。するとワード線とビット線の交点(クロスポイント)に等しい面積で、1個のメモリセルを構成できる。原理的にはこのアーキテクチャ(「クロスポイント・メモリ」と呼ぶ)が面積最小のメモリセルを実現可能である。

クロスポイント・メモリには、メモリセルアレイの積層が可能だという特長がある。そこで大容量抵抗変化メモリの研究開発では、アーキテクチャにクロスポイント・メモリを採用し、複数のメモリセルアレイを積み重ねることで製造コスト当たりの記憶容量を増やすという方向が主流になっている。ここで鍵となるのが、2端子のセレクタ技術である。なぜならば、3端子のトランジスタと違い、2端子のセレクタは良好なスイッチング特性を得ることが難しい。このため、さまざまなスイッチング技術が2端子のセレクタの候補技術となっている。

(次回に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

関連記事

TSMC、3nmチップの工場建設計画を発表

TSMC、3nmチップの工場建設計画を発表

TSMCが5nmおよび3nmチップの製造工場を新たに建設する計画を発表した。大手ファウンドリー各社のプロセス開発競争は激化の一途をたどっている。 まるで“空飛ぶプロセッサ”、進化する中国ドローン

まるで“空飛ぶプロセッサ”、進化する中国ドローン

商用、ホビー用ともにドローン市場で大きなシェアを持つ中国DJI。そのドローンの進化には、目を見張るほどだ。2016年前半に発売された「Phantom 4」には、実に90個を超えるチップが使われている。 ルネサス、フィン構造のMONOSフラッシュを開発

ルネサス、フィン構造のMONOSフラッシュを開発

ルネサス エレクトロニクスが、フィン構造を採用したSG(Split-Gate型)-MONOSフラッシュメモリセルの開発に成功したと発表した。フィン構造としたことで、FinFETなど先端のロジックプロセスとの親和性が高くなり、次世代の16nm/14nm世代マイコンに混載できるようになる。 IEDMで発表されていた3D XPointの基本技術(前編)

IEDMで発表されていた3D XPointの基本技術(前編)

米国で開催された「ISS(Industry Strategy Symposium)」において、IntelとMicron Technologyが共同開発した次世代メモリ技術「3D XPoint」の要素技術の一部が明らかになった。カルコゲナイド材料と「Ovonyx」のスイッチを使用しているというのである。この2つについては、長い研究開発の歴史がある。前後編の2回に分けて、これらの要素技術について解説しよう。 不揮発SRAMでプロセッサの待機時電力を大幅削減

不揮発SRAMでプロセッサの待機時電力を大幅削減

東京工業大学の菅原聡准教授らによる研究グループは、マイクロプロセッサの待機時電力を大幅に削減できる技術を開発した。低消費電力技術(パワーゲーティング)に不揮発性SRAMを用いることで実現した。 富士通セミ、CNT応用メモリ「NRAM」を商品化へ

富士通セミ、CNT応用メモリ「NRAM」を商品化へ

富士通セミコンダクターは2016年8月、Nantero(ナンテロ)とともに、カーボンナノチューブ(CNT)応用型不揮発メモリ「NRAM」の商品化に向けた開発を実施すると発表した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(前編)

- Rapidus、IIM-1を「世界初の前/後工程一貫工場に」

- 石炭灰から「レアアース元素」を回収、新日本繊維【訂正あり】

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(後編)

- 「27年度後半の2nm量産誓う」 Rapidus、解析センター開設

- EVに吹く逆風 デンソーの焦りとロームが求める勝機とは

- 経産省、Rapidusに6315億円追加支援 「国益のため必ず成功」

- 光電融合チップレットの技術開発を開始 LSTCとimec

- 京セラ、ウシオ電機の半導体レーザー事業を取得へ

- 「技術を束ねて高価値システムに」 デンソーが2030年中計発表