SanDiskが語る、抵抗変化メモリのセルアレイとセルの選択:福田昭のストレージ通信(52) 抵抗変化メモリの開発動向(11)(1/2 ページ)

今回は、半導体メモリのメモリセルアレイと、アレイから特定のメモリセルを選択する手段について説明する。

メモリセルからメモリセルアレイへの飛躍

半導体メモリの研究開発に関する国際学会「国際メモリワークショップ(IMW:International Memory Workshop)」のショートコース(2016年5月15日)から、SanDiskによる抵抗変化メモリ(ReRAM)の研究開発動向に関する講演概要をご紹介している。今回はシリーズの11回目に相当する。

| 抵抗変化メモリの開発動向バックナンバー: | |

|---|---|

| (1) | SanDiskが語る、半導体不揮発性メモリの開発史 |

| (2) | SanDiskが語る、コンピュータのメモリ階層 |

| (3) | SanDiskが語る、ストレージ・クラス・メモリの概要 |

| (4) | SanDiskが語る、ストレージ・クラス・メモリの信頼性 |

| (5) | SanDiskが語る、抵抗変化メモリの多様な材料組成 |

| (6) | SanDiskが語る、抵抗変化メモリの消費電流と速度 |

| (7) | SanDiskが語る、抵抗変化メモリの電気伝導メカニズム |

| (8) | SanDiskが語る、抵抗変化メモリのスイッチングモデル |

| (9) | SanDiskが語る、抵抗変化メモリの長期信頼性 |

| (10) | SanDiskが語る、抵抗変化メモリの抵抗値変化 |

講演者はスタッフエンジニアのYangyin CHEN氏、講演タイトルは「ReRAM for SCM application」である。タイトルにあるSCMとはストレージ・クラス・メモリ(Storage Class Memory)の略称で、性能的に外部記憶装置(ストレージ)と主記憶(メインメモリ)の間に位置するメモリとされる。ここで性能とは、メインメモリよりもコスト(記憶容量当たりのコスト)が低く、ストレージよりも高速であることを意味する。

本シリーズの10回目である前回は、抵抗変化メモリの抵抗値が書き込み後に変化する現象(リラクゼーション)を紹介した。今回は、半導体メモリの基本技術であるメモリセルアレイと、アレイから特定のメモリセルを選択する手段を説明する。

メモリセルを2次元の行列(マトリクス)状に並べる

半導体メモリは大抵、数多くのメモリセルを2次元の行列(マトリクス)状に並べることで、大量のデータ(ビット)を記憶する。この2次元マトリクス状に配置されたメモリセル群を、「メモリセルアレイ」と呼ぶ。

データを読み出したり、データを書き込んだりするときは、メモリセルアレイの中から、特定のメモリセルを選択する。具体的には、行(ロウ)の選択線(ワード線)と列(カラム)の選択線(ビット線)の交点に存在するメモリセルを、特定のワード線とビット線をアクティブ(電圧をオン)にすることで、指定する。

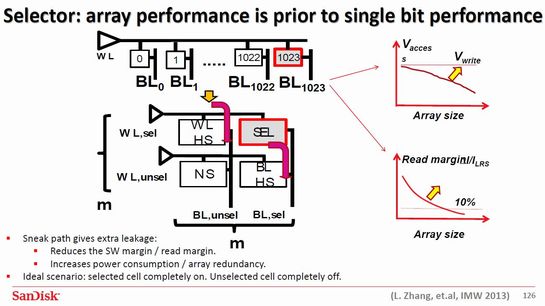

ここで重要なことは、半導体メモリの性能を決めるのは、メモリセル単体の性能ではなく、メモリセルアレイ全体の性能であることだ。言い換えると、最も性能の低い、あるいは低速のメモリセルが、半導体メモリの性能を決める。1本のワード線には複数のメモリセルが接続されているので、例えば、ワード線のドライバから最も近いメモリセルと最も遠いメモリセルでは、当然ながら、遅延時間に差が生じる。ドライバに最も近いメモリセルは遅延時間が最も短く、最も遠いメモリセルは遅延時間が最も長い。またワード線の配線抵抗によって電圧降下が生じるので、ワード線ドライバに遠いメモリセルでは、読み出しのマージン(雑音余裕)が低下する。

メモリセルアレイとメモリセルの選択。左上は1本のワード線に接続された1024個のメモリセルが選択される様子。1023番のメモリセル(右端のメモリセル)が選択されている。左下はワード線とビット線によってm行m列のマトリクスから特定のメモリセル(「SEL」とあるセル)を指定する様子。隣接するメモリセル(「WLHS」「BLHS」とあるセル)にも電圧が加わるため、別の電流経路(スニーク・パス)が生じることがある。出典:SanDisk(クリックで拡大)

メモリセルアレイとメモリセルの選択。左上は1本のワード線に接続された1024個のメモリセルが選択される様子。1023番のメモリセル(右端のメモリセル)が選択されている。左下はワード線とビット線によってm行m列のマトリクスから特定のメモリセル(「SEL」とあるセル)を指定する様子。隣接するメモリセル(「WLHS」「BLHS」とあるセル)にも電圧が加わるため、別の電流経路(スニーク・パス)が生じることがある。出典:SanDisk(クリックで拡大)メモリセル(記憶素子)のアレイとワード線、ビット線だけで、特定のメモリセルは選択可能である。ここで問題となるのは、ワード線を共用するメモリセルと、ビット線を共用するメモリセルにも、電圧が加わることだ。すると選択すべきメモリセルに隣接する2個のメモリセルを通して、余計な電流経路(スニーク・パス)が生じ、電流が余分に流れる。この雑音電流を「スニーク電流」と呼ぶ。

スニーク電流を防ぐ手段は、記憶素子とは別に、メモリセルを選択するスイッチをメモリセルごとに設けることである。このセル選択用スイッチ素子を「セレクタ」と呼ぶ。オンになったワード線とオンになったビット線の交点に存在するセレクタだけが、オンになる。こうすることで、スニーク電流の発生を防ぐ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増