ルネサス、65nmSOTBで低消費/高速の内蔵SRAM:読み出し速度2.5倍(1/2 ページ)

ルネサス エレクトロニクスは、SOTB(Silicon On Thin BOX)プロセス技術を用いた、ASSP向け低消費電力SRAMを試作した。基板バイアスを制御することにより、極めて小さいスタンバイ電力と高速読み出し動作を実現する。

IoT機器やヘルスケア機器向けASSPなどに適用

ルネサス エレクトロニクスは2017年6月8日、SOTB(Silicon On Thin BOX)プロセス技術を用いた、ASSP向け低消費電力SRAMを試作したと発表した。基板バイアスを制御することにより、極めて小さいスタンバイ電力と高速読み出し動作を両立することに成功した。

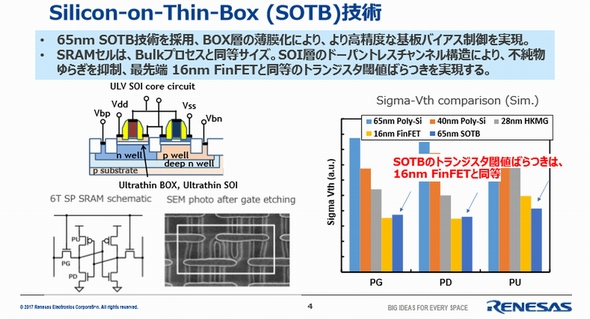

独自開発を進めているSOTBプロセス技術は、ウエハー基板上の薄膜シリコン層の下に、埋め込み酸化膜層(BOX:Buried Oxide)を形成した構造である。薄膜シリコン層に不純物を注入する必要のないドーパントレスチャネル構造のトランジスタを作成することができる。素子の特性ばらつきを抑え、オン電流とオフ電流の比率改善に優れているなどの特長がある。

ドーパントレスチャネル構造のトランジスタは、一般的にプレーナ型バルク構造のトランジスタに比べて、しきい値ばらつきを約3分の1に低減することができるという。この値は16nm FinFETデバイスと同等であり、0.5V程度の低電圧でも安定した動作を実現できる。

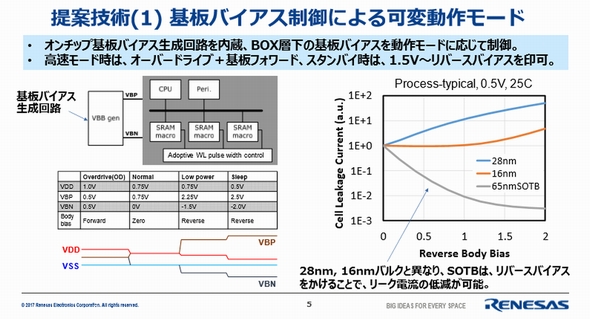

BOX層を薄くしたことで、BOX層下部のシリコン基板電位をより高い精度で制御し、トランジスタのしきい値特性を変更することが可能である。今回、65nmプロセスノードを用いて試作したSRAMは、基板バイアスを動的に制御するためのオンチップレギュレーター回路も備えた。基板バイアスを制御することによって、「通常モード」「低電力モード」「高速モード」と3つの動作モードおよび、「スタンバイモード」を選択することができる。

基板電位をゼロバイアスから順バイアスへ動的に制御し、動作モードを「通常」から「高速」に切り替えると、4.58ナノ秒であった読み出しアクセス時間が、1.84ナノ秒へと高速になる。この数値は、クロック周波数で380MHzに相当する。従来の通常モードに比べて2.5倍も高速である。

一方、スタンバイモードでは基板電位に逆バイアスを印加する。これにより、スタンバイ時の消費電力は13.7nW/Mビットと極めて小さくなる。この数値は、従来技術に比べて半分以下だという。アクティブ動作時の消費電力に比べると1000分の1となる。同社は「世界最小のスタンバイ特性」と主張する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待