EE Times Japan >

プロセス技術 >

ルネサス、65nmSOTBで低消費/高速の内蔵SRAM:読み出し速度2.5倍(2/2 ページ)

» 2017年06月08日 13時30分 公開

[馬本隆綱,EE Times Japan]

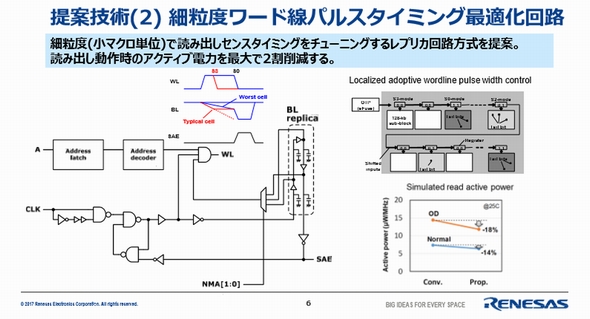

電力削減へ「レプリカ回路方式」

電力削減に向けて、同社が提案するもう1つの技術は「レプリカ回路方式」である。小さいマクロ単位でワード線の読み出しパルスタイミングを最適化する技術である。複数のSRAMマクロをチップ内に集積する場合、メモリセルごとに特性ばらつきが生じる。このため、一般的には最も特性ばらつきが大きいメモリセルに合わせてチップ全体のタイミングを決め、確実に動作するよう設計マージンを確保する必要があった。ところがこの方式だと、オーバーマージンになるメモリセルも存在することになる。

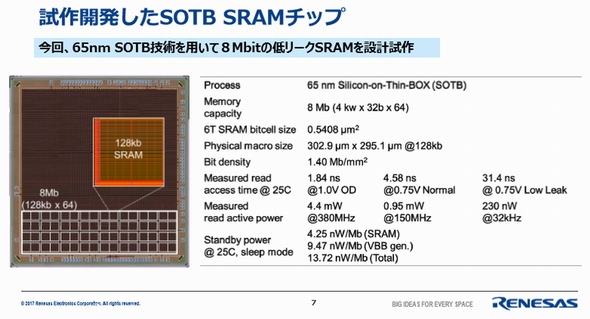

試作したSOTB構造のSRAMは、65nmプロセスノードを用いて、128Kビットのマクロを64個集積している。マクロの粒度(ビット数)は1ビット単位で選択することができるが、今回は128Kビット単位で、タイミングを最適化した。これによって過剰な設計マージンを除去することが可能となり、読み出し動作時のアクティブ電力を最大20%も削減することができたという。

ルネサス エレクトロニクスは、開発した65nmプロセスの内蔵SRAMをASSPに実装し、2018年3月からサンプル出荷を始めたい考えだ。量産時期は2019年3月を見込む。まずは、バッテリーレスやメンテナンスフリーなどが要求されるIoT機器や家庭用電子機器、ヘルスケア機器などに向けたASSPに、開発したSRAM技術を組み込んでいく。

なお、今回の開発成果は、2017年6月5日より京都で開催されている「VLSIシンポジウム国際会議(VLSI Symposia 2017)」で6月8日に発表した。

関連記事

ソニー、裏面照射で小型高精度ToFセンサー実現

ソニー、裏面照射で小型高精度ToFセンサー実現

ソニーは2017年6月5日、10μm角画素の裏面照射型Time of Flight(ToF)方式距離画像センサーを開発したと発表した。 2016年マイコンシェア、NXPがルネサスを抜き首位に

2016年マイコンシェア、NXPがルネサスを抜き首位に

IC Insightsが発表した2016年のマイコン(MCU)市場売上高ランキングによると、NXP Semiconductorsがルネサス エレクトロニクスを抜いて首位に立った。 ルネサスの「レベル4対応自動運転車」に試乗

ルネサスの「レベル4対応自動運転車」に試乗

ルネサス エレクトロニクスは、自動運転レベル4に対応する自動運転車の試乗会を東京都内で行った。安全な自動走行に加えて、「半導体の故障」や「サイバー攻撃」にも対応する機能を搭載している。 ルネサス、インターシル買収に伴い組織再編

ルネサス、インターシル買収に伴い組織再編

インターシルを買収したルネサス エレクトロニクスは2017年3月3日、事業組織を2017年7月までに段階的に改変すると発表した。インターシル買収で事業規模拡大を見込む汎用半導体を専門に扱う事業本部などを設ける。 ルネサス、組み込み向け仮想化技術をR-Carで実現

ルネサス、組み込み向け仮想化技術をR-Carで実現

ルネサス エレクトロニクスは、車載コンピューティングプラットフォーム「R-Car」用に、仮想化OS向けソフトウェアパッケージの提供を始めた。車両のセキュリティと機能安全を単一システム上で実現できるとする。 応用例で見る、ルネサスの組み込みAI

応用例で見る、ルネサスの組み込みAI

AI(人工知能)機能を持つ組み込み機器の登場が、スマートな社会を身近なものとする。ルネサス エレクトロニクスはセキュアで自律的に動作する組み込み機器を開発するための「e-AIソリューション」を提案する。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

Special SitePR

あなたにおすすめの記事PR