IBM、5nmナノシートで画期的成果を発表:FinFET代替なるか(1/2 ページ)

IBMなどが積層シリコンナノシートをベースにした新しいトランジスタ(シリコンナノシートトランジスタ)アーキテクチャを開発した。5nmノードの実現に向けて、FinFETに代わる技術として注目される。

FinFETと比べて消費電力を大幅に削減可能

IBMの研究チームは、パートナー企業と共に、積層シリコンナノシートをベースにした新しいトランジスタ(シリコンナノシートトランジスタ)アーキテクチャを開発したと発表した。5nmノードの実現に向けて、FinFETに代わる技術として適用できるという。

同アーキテクチャは2017年6月5日、京都で開催された半導体の回路技術に関する国際学会「2017 Symposia on VLSI Technology and Circuits」(2017年6月5〜8日)で発表された。研究アライアンスパートナーであるGLOBALFOUNDRIESとSamsung Electronics、製造装置メーカーらとの約10年にわたるナノシートの研究の末、開発に成功したという。同アーキテクチャは、FinFETと比べて消費電力を大幅に削減できるという。

シリコンナノシートトランジスタによって、スマートフォンなどのモバイル機器は1回のバッテリー充電で2〜3日間動作できるようになるという。また、性能が大きく向上することから、AI(人工知能)やVR(仮想現実)、スーパーコンピュータ(スパコン)への活用も期待できるとする。

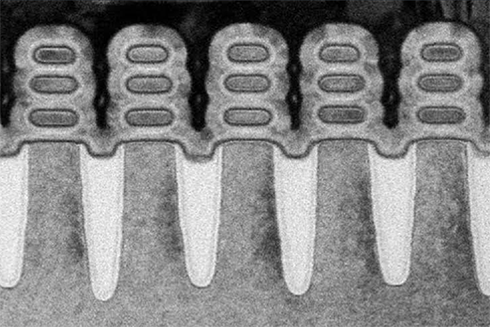

同研究アライアンスは、200億個のトランジスタを搭載した7nmプロセスのテストチップを開発してから2年もたたずして、爪の先ほどのサイズのチップに300億個のトランジスタを搭載することに成功した。同トランジスタは、ナノワイヤをゲート電極で取り囲むGAA(Gate-All-Around)構造を採用したものだ。テスト結果では、同じ電力の7nm FinFETに比べて、性能が40%向上したという。さらに、10nmプロセスのトランジスタに比べると消費電力を最大75%削減できるとした。

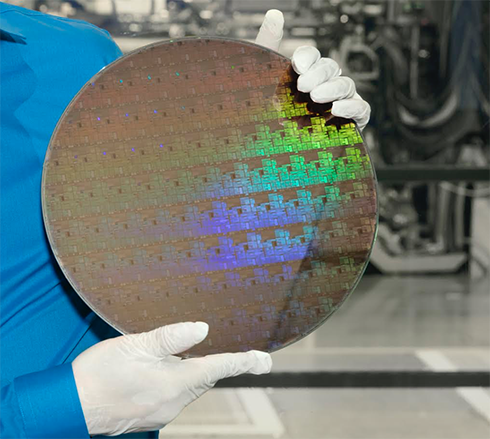

シリコンナノシートを採用したトランジスタを構築したウエハー。ウエハーを持っているのは、IBM Researchの研究員であるNicolas Loubet氏(クリックで拡大) 出典:IBM、写真:Connie Zhou氏

シリコンナノシートを採用したトランジスタを構築したウエハー。ウエハーを持っているのは、IBM Researchの研究員であるNicolas Loubet氏(クリックで拡大) 出典:IBM、写真:Connie Zhou氏IBMは、「5nmの実現に向けたこの新技術は、チップの性能を大きく向上するため、コグニティブコンピューティングや、より高いスループットを実現するクラウドコンピューティング、ディープラーニングにも貢献できると期待している。また、IoT(モノのインターネット)に必要な低消費電力、長時間バッテリー駆動という特長も備えている」と説明している。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待