EE Times Japan >

プロセス技術 >

IBM、5nmナノシートで画期的成果を発表:FinFET代替なるか(2/2 ページ)

» 2017年06月12日 10時50分 公開

[R. Colin Johnson,EE Times Japan]

ナノシートの幅を調整

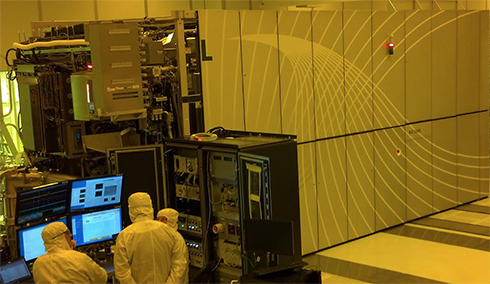

同研究アライアンスは、この技術的革新を達成するために、7nm FinFETチップで導入されるとみられているEUV(極端紫外線)リソグラフィの課題を克服しなくてはならなかった。同アライアンスは、EUVの短波長というメリット以外に、半導体の設計と製造の両方の工程でナノシートの幅を調整する方法を発見したという。

IBMは、「ナノシートアーキテクチャは、シングルセルDRAMのプロセス技術のブレイクスルーや、化学増幅型レジスト、銅ワイヤボンディング、SOI(シリコン・オン・インシュレータ)、歪み材料、マルチコアプロセッサ、液浸リソグラフィ、高誘電率材料、組み込みDRAM、3次元(3D)積層チップ、エアギャップインシュレータと並ぶ画期的技術だ」と主張している。

GLOBALFOUNDRIESのCTO(最高技術責任者)でワールドワイドR&D部門のリーダーを務めるGary Patton氏は、同アーキテクチャを“非常に画期的な技術”とアピールし、5nm以降の次世代プロセス技術の実現に向けて積極的に研究を続けていく姿勢を明らかにした。

【翻訳:滝本麻貴、編集:EE Times Japan】

関連記事

「ムーアの法則は終わった」、NVIDIAのCEOが言及

「ムーアの法則は終わった」、NVIDIAのCEOが言及

台湾・台北で開催された「COMPUTEX TAIPEI 2017」で、NVIDIAのCEOであるJensen Huang氏は、「ムーアの法則は終わった。マイクロプロセッサはもはや、かつてのようなレベルでの微細化は不可能だ」と、ムーアの法則の限界について言及した。 EUVと液浸、FinFETとFD-SOI、GFの強みは2点張り

EUVと液浸、FinFETとFD-SOI、GFの強みは2点張り

2017年5月31日、来日したGLOBALFOUNDRIES(グローバルファウンドリーズ/GF)CMOSプラットフォーム事業部シニアバイスプレジデントのGregg Bartlett氏に7nm FinFET、12nm FD-SOIの開発状況などについてインタビューした。 Samsung、2020年に4nmのリスク生産を開始

Samsung、2020年に4nmのリスク生産を開始

Samsung Electronicsは、ファウンドリー技術のロードマップを発表した。2020年に4nmプロセスを用いて、同社独自の「MBCFET(Multi Bridge Channel FET)」のリスク生産を開始する予定だという。 ムーアの法則は健在! 10nmに突入したGalaxy搭載プロセッサの変遷

ムーアの法則は健在! 10nmに突入したGalaxy搭載プロセッサの変遷

今回はSamsung Electronicsの最新スマートフォン「Galaxy S8+」に搭載されているプロセッサ「Exynos8895」を中心に、Galaxy Sシリーズ搭載プロセッサの進化の変遷を見ていく。そこには、ムーアの法則の健在ぶりが垣間見えた。 IMECの半導体ロードマップ展望

IMECの半導体ロードマップ展望

IMECのプロセス技術関連のベテラン専門家であるAn Steegen氏が、2017年の半導体ロードマップを発表し、半導体プロセスの微細化に対し楽観的な見方を示した。 ムーアの法則、半導体業界はどう捉えるべきか(前編)

ムーアの法則、半導体業界はどう捉えるべきか(前編)

台湾Etron TechnologyのCEOであるNicky Lu氏は、「ムーアの法則」は、技術開発の方針としての役目を既に終え、ビジネス的な意味合いの方が強くなっていると述べる。半導体メーカーが今、ムーアの法則について認識すべきこととは何なのか。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

Special SitePR

あなたにおすすめの記事PR