データセンター向け技術をオープンに、進む取り組み:Microsoftなどが主導(2/3 ページ)

データ圧縮アルゴリズムやRoot of Trustのプロジェクトも

最近発表されたある研究によると、1年間のデータ量は2025年までに、175ZB(ゼタバイト)に達する見込みだという。これを受けて始動したのが、データ圧縮アルゴリズム「Project Zipline」だ。データセンター向けに最適化し、パターンマッチングIP(Intellectual Property)ブロックに実装された、ハフマンエンコーディングの変化を定義する。Microsoftからのテストファイルを大幅に圧縮しながら、10ギガバイト/秒単位のスループットで、マイクロ秒レベルのレイテンシに対応することが可能だ。

Vaid氏は、「新しい圧縮技術の開発には、かなりの時間を要する」との認識を示している。現在のところ、Project Ziplineを支持する企業には、AMDやArm、Broadcom、Cadence、Intel、Marvell Technology Group、Mellanox、Synopsysなどが名を連ねている。

またOCPは、この他にも別のプロジェクト「Project Cerberus」において、プロセッサの信頼の基点(Root of Trust)をサーバの全てのデバイスへと拡大しようとしている。そのためには、FacebookやIntel、Microsoftなどのグループによって定義される、新しいプロトコルとIPブロックが必要になる。

この手法では、既存のCerberusマザーボードで使われているコントローラーをマスターとし、周辺チップのスレーブブロックとやりとりする。Intelの広報担当者は、「OCPは、この周辺ブロックをオープンソース化する可能性がある」と述べている。

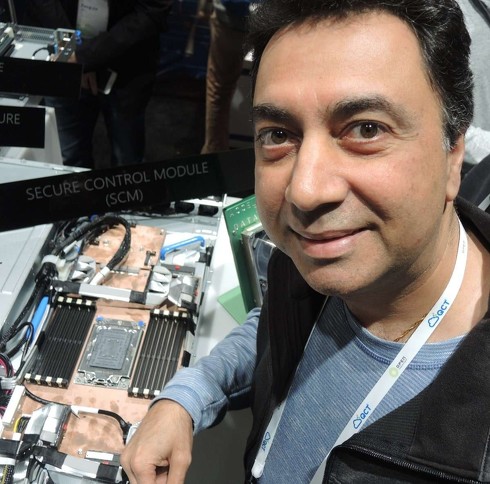

Microsoftのエンジニアは、手掛けているプロジェクトについて、「サーバのマザーボードをモジュールに分割することにより、コストの低減と設計期間の短縮の実現を目指す」と説明している。プロジェクトリーダーを務めるSiamak Tavallaei氏は既に、コンセプトに関する高水準記述を発表しており、2019年夏までにプロトタイプを開発することに関心を持っている、十数社の企業から支持を得ているという。

これらの取り組みにより、プロセッサとメモリを1つのモジュールに統合することが可能になるという。さまざまな種類のCPUブロックでセキュアなコントローラーモジュールを使用することにより、ファームウェアの動作や、温度の監視、ファンの制御など、さまざまな基本的作業を実行することができる。

また、現在PCIe Gen 4をベースとしているI/Oケーブルを使用することで、ボードスペースを縮小し、プロセッサとI/Oをできるだけ近づけることが可能になる。これにより、PCB材料を最大60%削減し、ポートやPCIeスロットの他、GPUなどのアクセラレータ向けとして、シャシーのスペースを確保できるようになるという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- Musk氏は「半導体製造の再定義」を目指すのか

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- 世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに

Siamak Tavallaei氏

Siamak Tavallaei氏