光トランシーバーのForm Factor規格(その3)〜800G、そしてその先へ:光伝送技術を知る(11)光トランシーバー徹底解説(5)(1/3 ページ)

光トランシーバーのForm Factor規格を紹介する第3回。今回は、800G光トランシーバーなどについてまとめる。

前回に続き、光トランシーバーの主なForm Factor規格をまとめる。

(7)800G光トランシーバーForm Factor

現在のデータ交換量の爆発的増加は続くことが予測される中、400G以後を目指した議論が既に始まっている。

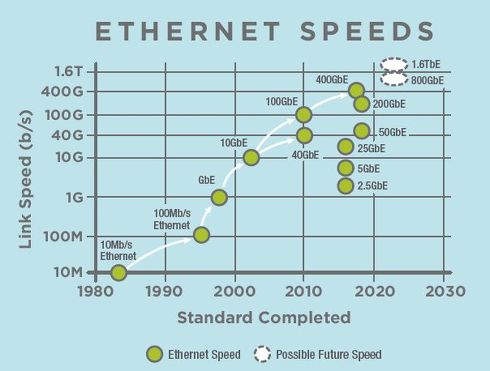

IEEE 802.3では、2018年9月からIEEE 802.3 NEA (New Ethernet Application) Ad Hocにおいて“Bandwidth Assessment (BWA)”が開始され、“Beyond 400GbE”へのCFIがことし(2020年)1月に提案された。この段階では、800Gなのか1.6Tなのか、または両方なのかは含みを持たせている。

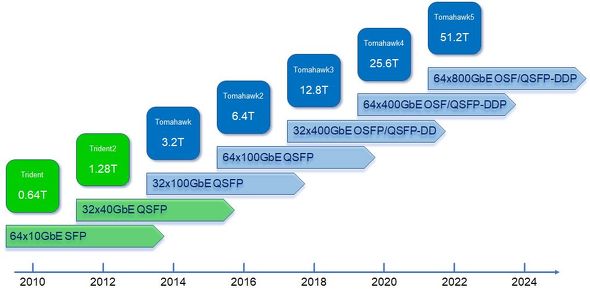

一方、Broadcomが製品化してきたスイッチICの交換容量が、2年ごとに2倍になるというトレンドがよく知られている。2019年末に25.6Tの交換容量のある「Tomahawk4」が製品発表された。このトレンドが続くとしたら2022年に51.2TのIC(Tomahawk5?)が市場に出て光インタフェースも800G、あるいは1.6Tが必要になってくる(図1)。

Ethernet Allianceの「2020 Roadmap」では、将来Service ProvidersやCloud Providersにおいては800Gそして1.6Tへ移行するとして、2022年から2023年にそれらが規格化されると予測している(図2)。

これに対し、800Gの実現に向けた活動が始まっている。光インタフェースとForm FactorのMSAが2019年9月に発足した。

800G Pluggable MSAは、データセンター内配線(<2km)の光インタフェース規格化を目指す。名称通り、Pluggableトランシーバーで可能な短距離の規格を議論している。基本的にQSFP-DDのForm Factorを念頭に置いて、光インタフェースの規格化議論が行われている。Webサイトによれば、IMDD(Intensity Modulation/Direct Detection)方式を採用するようだ。本稿はForm Factorに関するものなので光インタフェースは別の機会に報告したい。

400Gで競っているQSFP-DDもOSFPも高速電気信号は8本であり、現在OIFで議論されているOIF-CEI-112Gを用いることで800Gトランシーバーを実現できる。

2019年9月に結成されたQSFP-DD800は、2020年3月6日にその仕様を発表した。もちろん100G QSFP、400G QSFP-DDとのバックワードコンパティビリティを有利な点としている。カードエッジの高速信号パタンはピッチ0.80mm、線幅0.45mmである。

これに対し、OSFP MSAは2020年3月14日、現行の仕様で800Gが可能だと発表した。カードエッジの高速信号パタンはピッチ0.60mm、線幅0.38mmである。

【QSFP-DD800】

400G QSFP-DD同様、Type1とType2が定義されている。新たに追加された主な項目は、カードエッジを100G電気インタフェースに高速化したことと、同軸ケーブルを使用したケージ(+電気コネクター)を採用したことである。

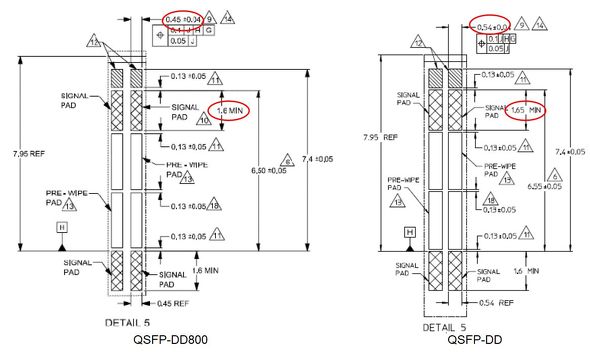

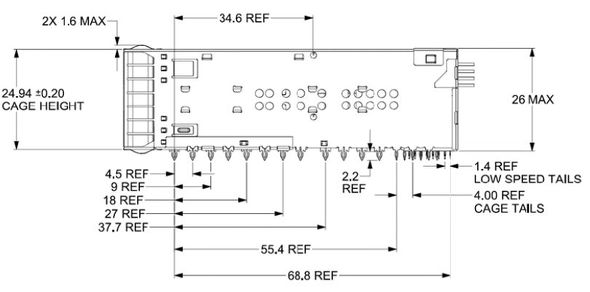

高速化に伴い、カードエッジのパッドパタン寸法が、400G QSFP-DDに対するコンパティビリティを保ちながら仕様化された。ピッチはQSFPと同じ0.80mmとしつつ、QSFP-DD800ではパタン幅を0.45mmとした(ちなみにQSFP-DDは0.54mm)。これによって400G QSFP-DD規格のケージとコネクターが使用できるようになっている。

100Gの電気インタフェースであるOIF-CEI-112Gは規格化の途中であり、電気インタフェースは「100G per electrical lane」としか記述されていない。しかし、カードエッジ仕様は112Gbit/s PAM4、つまり56GBaudの帯域を前提にしていると推測される。

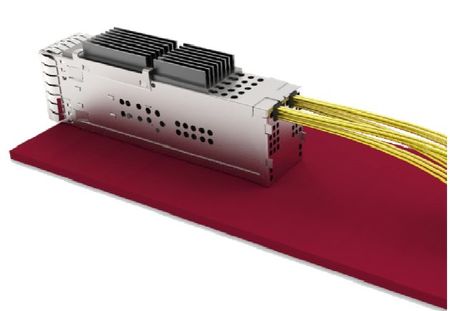

さらに、新たに2個のトランシーバーを上下に挿入できる2階建ケージ/コネクターで上階の接続に同軸ケーブルを使った規格が追加された。100Gbit/s電気インタフェースは、より接続距離が短くなることから、PCBからの距離が遠い上階での信号帯域の劣化が懸念される。そこで伝送損失の小さい同軸ケーブルを用い、IC近辺から直接接続することで帯域を確保する方式である。また、EMIシールド強化とヒートシンク構造を提案し、24Wまで対応できるとしている。

| 項目 | 説明 |

|---|---|

| 規格文書 | QSFP-DD800 MSA/ |

| 光インタフェース | Dual LC MPO-12、-16、2x12 CS connector Quad MDC connector Quad SN connector |

| 電気インタフェース | 60-pinカードエッジ・パターンは高速化のため高速信号パタン幅0.45mm(図3) トランシーバーピン配置はQSFP-DDと同じ |

| 機械的仕様 | モジュール外形仕様はQSFP-DDと同じ コネクターはQSFP-DDと同じ モジュールを挿入するケージは、QSFP-DDに加え2階建の上階に同軸ケーブル接続を追加(図4、5) |

| 管理インタフェース | CMIS |

| その他 | 24Wを許容したヒートシンク構造(図6) |

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

図3 QSFP-DD800カードエッジ高速信号パッド寸法

図3 QSFP-DD800カードエッジ高速信号パッド寸法 図4 追加された同軸ケーブル接続の2段ケージコネクター

図4 追加された同軸ケーブル接続の2段ケージコネクター 図5 追加された上段コネクター付きケージ

図5 追加された上段コネクター付きケージ 図6 EMI強化とヒートシンク構造

図6 EMI強化とヒートシンク構造